FPGA课程设计报告汇编Word文档格式.docx

FPGA课程设计报告汇编Word文档格式.docx

- 文档编号:13469607

- 上传时间:2022-10-11

- 格式:DOCX

- 页数:15

- 大小:384.24KB

FPGA课程设计报告汇编Word文档格式.docx

《FPGA课程设计报告汇编Word文档格式.docx》由会员分享,可在线阅读,更多相关《FPGA课程设计报告汇编Word文档格式.docx(15页珍藏版)》请在冰豆网上搜索。

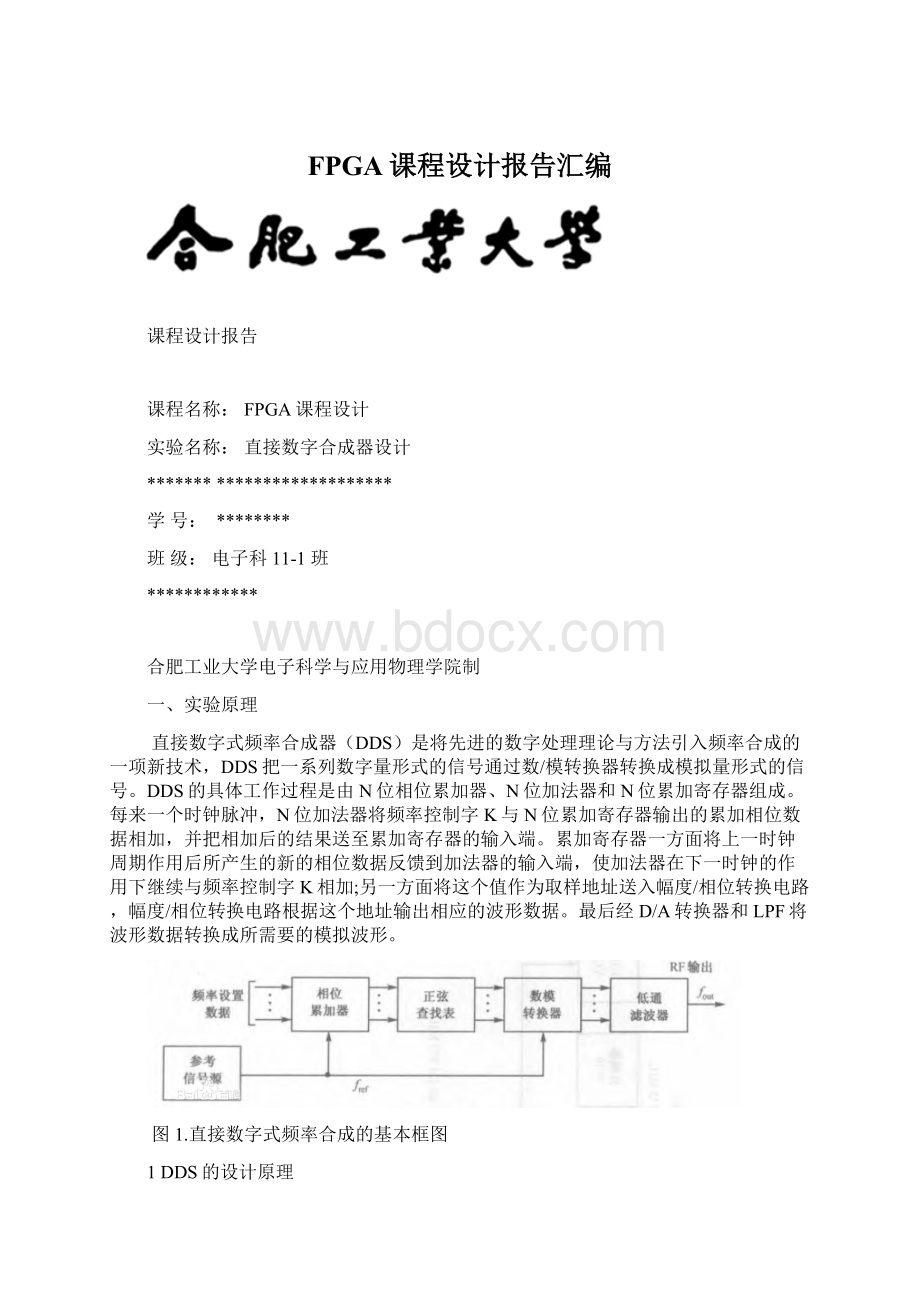

DDS的设计原理

DDS的原理图如图1所示。

DDS实现频率合成主要是通过查表的方式进行的。

正弦查询表是一个只读存储器(ROM),以相位为地址,存有1个或多个按0°

~360°

相位划分幅值的正弦波幅度信息。

相位累加器对频率控制字进行累加运算,若需要还可以加入相位控制字,得到的结果作为正弦波查询表的地址。

正弦查询表的输出为数字化正弦幅度值,通过D/A转换器转化为近似正弦波的阶梯波,再通过低通滤波器滤除高频成分和噪声最终得到一个纯正度很高的正弦波。

1.1

建模

正弦波y=sin(2πx),若以f量化的量化频率对其幅度值进行量化,一个周期可以得到M=f量化个幅度值。

将这些幅度值按顺序存入到ROM。

相位累加器在参考时钟的驱动下,每来1个脉冲,输出就会增加1个步长相位增量X,输出数据作为地址送入ROM中,读出对应的幅度值形成相应的波形。

1.2

参数设定

DDS输出信号频率:

其中,X为频率累加器设定值;

N为相位累加器位数;

fc为参考时钟频率。

例如,假定基准时钟为200

MHz,累加器的位数为32,频率控制字X为:

0x08000000H,即为227,则:

再设定频率控制字X为0x80000000H,即为231,则:

可见,理论上通过设定DDS相位累加器位数N、频率控制字X和基准fc的值,就可以得到任一频率的输出。

频率分辨率为:

fres=fc/2N,由参考时钟和累加器的位数决定,当参考时钟的频率越高,相位累加器的位数越高,所得到的频率分辨率就越高。

1.3

方案的选择

在利用FPGA制作DDS时,相位累加器是决定DDS性能的一个关键部分。

一方面可以利用进位链来实现快速、高效的电路结构,同时长的进位链会减少其他逻辑的布线资源,限制整个系统速度的提高;

另一方面可以利用流水线技术提高工作频率,但系统频率转换速度会相对降低。

在选择累加器实现方案时需要综合考虑。

正弦波查询表ROM也是制作的重点。

在FPGA中ROM表的尺寸随着地址位数或数据位数的增加呈指数递增,如何在满足性能的前提下节省资源开销。

一方面通过相位累加器的输出截断方式,例如从32位的相位累加器结果中提取高16位作为ROM的查询地址,由此而产生的误差会对频谱纯度有影响,但是对波形的精度的影响是可以忽略的;

另一方面可以根据信号周期对称性来压缩ROM的

尺寸,这时系统硬件设计复杂度会有所增加。

因此,需要选取合适的参数和ROM

压缩技术,在满足系统性能的前提下使得系统尽量优化。

二、实验步骤

2.VerilogHDL实现DDS模块

2.1累加器模块

累加器模块实现将相位控制字以及频率控制字累加,并生成地址输出,利用该地址可以对ROM寻址。

累加器模块的verilog程序如下:

moduleacc(clk,clr,dataa,datab,

addr);

input[11:

0]dataa,datab;

inputclk,clr;

output[11:

0]addr;

wire[11:

//reg[15:

0]daraa_reg,datab_reg;

reg[11:

0]A,addr_reg;

always@(posedgeclkorposedgeclr)

begin

if(clr)

addr_reg=16'

h0000;

A=16'

end

else

A=A+dataa;

addr_reg=datab+A;

end

assignaddr=addr_reg;

endmodule

2.2ROM的生成

制作DDS的过程中,我们需要正弦函数上各个点的具体数值,以便我们输出正弦波形,这些正弦波的数值需要存入一个只读寄存器(ROM)中。

在ise中可以通过添加ip核来生成ROM。

制作完成后可以在工程中看到生成的ROM如图2:

图2.

由于ROM数据较多我们需要利用matlab来完成COE文件的生成,

生成COE的程序如下:

assignaddr=addr_reg;

Endmodule

2.2ROM正弦查询表

用ISE创建ROM

Step1:

在ISE工程下生成一个ROM

Step2:

编写.coe文件,作为ROM的初始化文件

这一步与QuartusII不同,因为QuartusII中ROM的初始化文件为.mif或者.hex,而在ISE中ROM的初始化文件是.coe文件,所以需要编写.coe文件。

.coe文件的格式很简单,下面就是一个.coe文件的内容:

MEMORY_INITIALIZATION_RADIX=16;

//表示ROM内容的数据格式是16进制

MEMORY_INITIALIZATION_VECTOR=

0a,

0b,

0c;

//每个数据后面用逗号或者空格或者换行符隔开,最后一个数据后面加分号。

Step3:

利用ISE中的IP核生成工具生成ROM

在这次课程设计中,我们利用matlab生成COE文件,matlab的程序如下:

t=0:

2*pi/2^12:

2*pi

y=0.5*sin(t)+0.5;

r=ceil(y*(2^8-1));

%将小数转换为整数,ceil是向上取整。

fid=fopen('

sin.coe'

'

w'

);

%写到sin.coe文件,用来初始化sin_rom

fprintf(fid,'

MEMORY_INITIALIZATION_RADIX=10;

\n'

MEMORY_INITIALIZATION_VECTOR=\n'

fori=1:

1:

2^12

%d'

r(i));

ifi==2^12

;

'

else

ifi%15==0

fclose(fid);

2.3顶层模块设计:

顶层模块完成累加器的调用,以及ROM的调用,输出我们所需要的数据

顶层模块的程序如下:

moduletopmodel(clk,clr,ena,dataa,datab,dds_data

);

inputclk,clr,ena;

input[11:

output[15:

0]dds_data;

//reg[15:

0]result_reg;

wire[11:

0]result_wire;

//reg[12:

0]addr_reg;

//wire[12:

0]addr_wire;

accaccu(.clk(clk),.clr(clr),.dataa(dataa),.datab(datab),.addr(result_wire));

sinromwave(

.clka(clk),//inputclka

.ena(ena),//inputena

.addra(result_wire),//input[12:

0]addra

.douta(dds_data)//output[15:

0]douta

2.4测试文件的编写以及仿真

在完成程序的编写之后,需要添加测试文件以及激励信号,实现在电脑上仿真。

测试程序如下:

moduletesttop;

//Inputs

regclk;

regclr;

regena;

reg[11:

0]dataa;

0]datab;

//Outputs

wire[15:

//InstantiatetheUnitUnderTest(UUT)

topmodeluut(

.clk(clk),

.clr(clr),

.ena(ena),

.dataa(dataa),

.datab(datab),

.dds_data(dds_data)

initialbegin

//InitializeInputs

clk=0;

clr=1;

ena=0;

dataa=0;

datab=0;

//Wait100nsforglobalresettofinish

#6clr=0;

#5dataa=12'

h0003;

#1datab=12'

#10ena=1;

//#2ena=0;

//Addstimulushere

always#5clk=~clk;

always@(posedgeclk)

begin

$display("

%d"

dds_data);

end

2.5程序下载实现硬件仿真

实现程序的下载首先需要先设置cdc

图3.cdc设置

图4.cdc关联引脚

完成cdc设置之后需要进行ucf引脚约束文件的编写:

ucf文件内容如下:

NET"

clk"

LOC=AH15;

ena"

LOC=AC24;

clr"

LOC=AC25;

dataa[0]"

LOC=AE26;

dataa[1]"

LOC=AE27;

dataa[2]"

LOC=AF26;

data

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 课程设计 报告 汇编

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx