数字电路-触发器的功能测试实验报告Word格式文档下载.doc

数字电路-触发器的功能测试实验报告Word格式文档下载.doc

- 文档编号:13084948

- 上传时间:2022-10-04

- 格式:DOC

- 页数:5

- 大小:1.44MB

数字电路-触发器的功能测试实验报告Word格式文档下载.doc

《数字电路-触发器的功能测试实验报告Word格式文档下载.doc》由会员分享,可在线阅读,更多相关《数字电路-触发器的功能测试实验报告Word格式文档下载.doc(5页珍藏版)》请在冰豆网上搜索。

触发器的功能测试

一、实验目的

(一)掌握基本RS触发器的功能测试。

(二)掌握集成触发器的电路组成形式及其功能。

(三)熟悉时钟触发器不同逻辑功能之间的相互转换。

(四)认识触发器构成的脉冲分频电路。

二、实验仪器:

DZX-1型电子学综合实验装置UT52万用表GDS-806S双踪示波器74LS0074LS7474LS76

三、实验内容&

数据分析

触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一种具有记忆功能的二进制信息存贮器件,是构成各种时序电路的最基本逻辑单元。

第一步,将触发器74LS74、74LS76引出端排列图和状态表画在实验报告上。

(注:

此项内容必须在进实验室前完成。

)

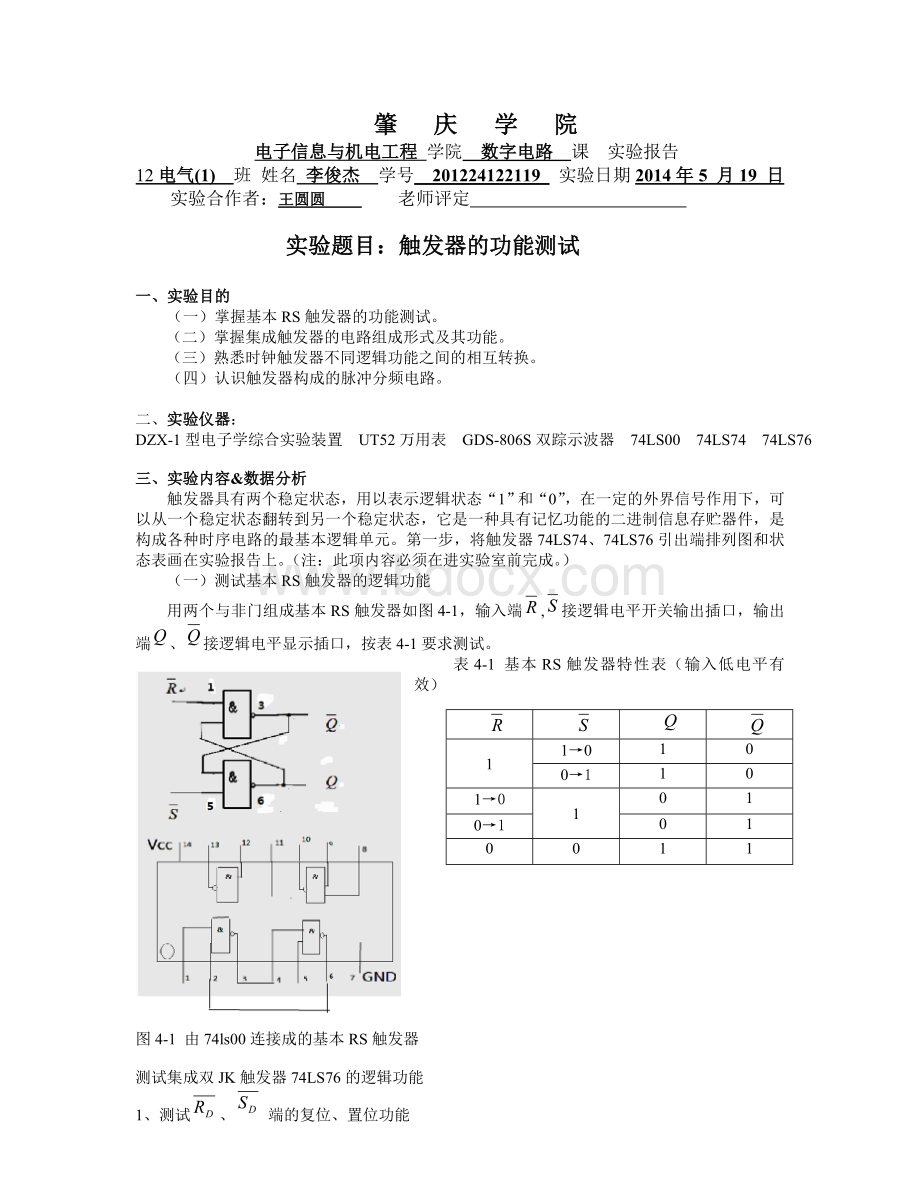

(一)测试基本RS触发器的逻辑功能

用两个与非门组成基本RS触发器如图4-1,输入端,接逻辑电平开关输出插口,输出端、接逻辑电平显示插口,按表4-1要求测试。

表4-1基本RS触发器特性表(输入低电平有效)

1

1→0

0→1

图4-1由74ls00连接成的基本RS触发器

测试集成双JK触发器74LS76的逻辑功能

1、测试、端的复位、置位功能

74LS76逻辑符号如图4-2,对照其插脚(查阅附录B)取其中一JK触发器,、、J、K端分别接逻辑电平开关输出插口,CP接单次脉冲源(正脉冲),、接至逻辑电平显示输入插口。

要求在=0,=1以及=0,=1时任意改变J、K及CP的状态用“ⅹ”符号表示,观测、状态。

表4-2集成双JK触发器74LS76特性表1

CP

Q

图4-274LS76管脚排列

2、测试触发器的逻辑功能

按表4-2的要求改变J、K、CP端状态,记录Q的状态变化,观察触发器状态的更新发生在CP脉冲(单脉冲)的上降沿还是下降沿?

(注意、端的电平接法)

表4-3集成双JK触发器74LS76特性表2

J

K

图4-2JK触发器逻辑符号

3、JK触发器的J、K端连在一起,构成T’触发器。

在CP端输入1MHZ连续脉冲,用双踪示波器观察CP、Q端的波形,注意相位与时间的关系。

图4-3JK触发器构成T’触发器电路图及CP、Q端的波形图

(三)测试集成双D触发器74LS74的逻辑功能

1、74LS74逻辑符号如图4-3,对照其插脚,任取一只D触发器,按表4-3要求进行测试,并观察触发器状态的更新是在CP脉冲的上降沿还是下降沿?

(注意复位、置位端的电平接法)

表4-3集成双D触发器74LS74的特性表

D

上升沿有效

图4-4D触发器逻辑符号及74LS74引脚图

2、将D触发器的端与D端相连接,构成触发器。

测试方法同实验内容

(二)(3)。

图4-5D触发器构成触发器电路图

(四)JK触发器简单应用实验————电路构成及测试

实验电路照图4-6连接(注意复位、置位端的电平接法)。

时钟频率用时钟信号源的“Q7”,加到CP端,用示波器分别显示Q0、Q1和的波形,并把波形图画在实验报告中。

图4-7JK触发器Q0、Q1和的波形

分析D触发器和JK触发器,找出它们的相同点和不同点。

同:

两者都是由基本RS触发器构成的边沿触发器

异:

1、JK触发器有JK两个输入端,能实现保持、置零、置一、翻转功能

2、D触发器只有一输入端,能实现置零、置一功能

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电路 触发器 功能 测试 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

![1.15的乘法口诀[王芳]【市一等奖】优质课教案.doc](https://static.bdocx.com/images/filetype/d_word.png) 1.15的乘法口诀[王芳]【市一等奖】优质课教案.doc

1.15的乘法口诀[王芳]【市一等奖】优质课教案.doc