数字逻辑期末复习题Word格式.doc

数字逻辑期末复习题Word格式.doc

- 文档编号:13084934

- 上传时间:2022-10-04

- 格式:DOC

- 页数:37

- 大小:726.50KB

数字逻辑期末复习题Word格式.doc

《数字逻辑期末复习题Word格式.doc》由会员分享,可在线阅读,更多相关《数字逻辑期末复习题Word格式.doc(37页珍藏版)》请在冰豆网上搜索。

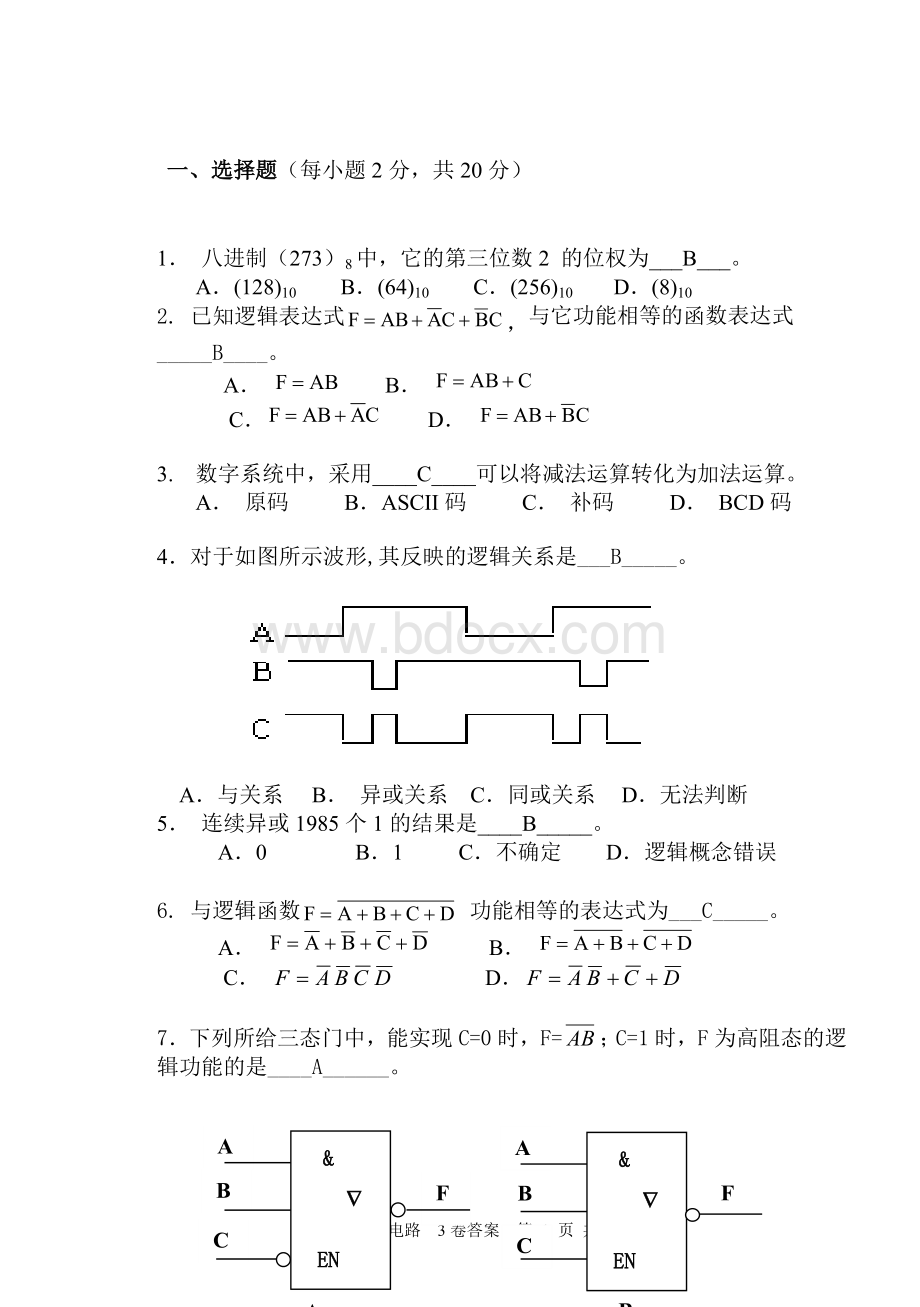

B

F

C

A

&

Ñ

EN

D

8.如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。

CP

Q

A.500KHzB.200KHz

C.100KHzD.50KHz

9.下列器件中,属于时序部件的是_____A_____。

A.计数器B.译码器C.加法器D.多路选择器

10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。

A.0100100B.1100011C.1011011D.0011011

共阴极LED数码管

ABCD

abcdefg

译码器

g

f

d

e

c

a

b

得分

评卷人

二、填空题(每小题2分,共20分)

11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2.4-5____V。

12.N个输入端的二进制译码器,共有_______个输出端。

对于每一组输入代码,有____1____个输出端是有效电平。

13.给36个字符编码,至少需要____6______位二进制数。

14.存储12位二进制信息需要___12____个触发器。

15.按逻辑功能分类,触发器可分为__RS___、__D__、__JK__、_T_等四种类型。

16.对于D触发器,若现态Qn=0,要使次态Qn+1=0,则输入D=__0_____。

17.请写出描述触发器逻辑功能的几种方式___特性表、特性方程、状态图、波形图_________。

18.多个集电极开路门(OC门)的输出端可以_____线与_______。

19.T触发器的特性方程是________,当T=1时,特性方程为________,这时触发器可以用来作___2分频器_____。

20.构造一个十进制的异步加法计数器,需要多少个__4____触发器。

计数器的进位Cy的频率与计数器时钟脉冲CP的频率之间的关系是____1﹕10_________。

三、分析题(共40分)

21.(本题满分6分)用卡诺图化简下列逻辑函数

解:

画出逻辑函数F的卡诺图。

得到

CD

AB

00

01

11

10

1

22.(本题满分8分)电路如图所示,D触发器是正边沿触发器,图中给出了时钟CP及输入K的波形。

(1)试写出电路次态输出逻辑表达式。

(2)画出的波形。

K

DQ

Q

=1

23.(本题满分10分)分析图示逻辑电路,求出F的逻辑函数表达式,化简后用最少的与非门实现之,并画出逻辑电路图。

解:

24.(本题满分16分)今有A、B、C三人可以进入某秘密档案室,但条件是A、B、C三人在场或有两人在场,但其中一人必须是A,否则报警系统就发出警报信号。

试:

(1)列出真值表;

(2)写出逻辑表达式并化简;

(3)画出逻辑图。

设变量A、B、C表示三个人,逻辑1表示某人在场,0表示不在场。

F表示警报信号,F=1表示报警,F=0表示不报警。

根据题意义,列出真值表

ABC

F

000

001

010

011

100

101

110

111

0

1

由出真值表写出逻辑函数表达式,并化简

画出逻辑电路图

≥1

四、综合应用题(每小题10分,共20分)

25.3-8译码器74LS138逻辑符号如图所示,S1、、为使能控制端。

试用两片74LS138构成一个4-16译码器。

要求画出连接图说明设计方案。

A2A1A0

S1S2S3

74LS138

Y7Y6Y5Y4Y3Y2Y1Y0

Y15

Y8

Y7

Y0

A3

A2

A1

A0

74138

解:

26.下图是由三个D触发器构成的寄存器,试问它是完成什么功能的寄存器?

设它初始状态Q2Q1Q0=110,在加入1个CP脉冲后,Q2Q1Q0等于多少?

此后再加入一个CP脉冲后,Q2Q1Q0等于多少?

Q2

DCI

Q1

Q0

时钟方程

激励方程

,,

状态方程

状态表

101

011

110

画出状态图

一、选择题

1.一位十六进制数可以用C位二进制数来表示。

A.1B.2C.4D.16

2.十进制数25用8421BCD码表示为B。

A.10101B.00100101C.100101D.10101

3.以下表达式中符合逻辑运算法则的是D。

A.C·

C=C2B.1+1=10C.0<

1D.A+1=1

4.当逻辑函数有n个变量时,共有D个变量取值组合?

A.nB.2nC.n2D.2n

5.A+BC=C。

A.A+BB.A+CC.(A+B)(A+C)D.B+C

6.在何种输入情况下,“与非”运算的结果是逻辑0。

D

A.全部输入是0B.任一输入是0C.仅一输入是0D.全部输入是1

7.以下电路中可以实现“线与”功能的有C。

A.与非门B.三态输出门C.集电极开路门D.CMOS与非门

8.以下电路中常用于总线应用的有A。

A.TSL门B.OC门C.漏极开路门D.CMOS与非门

9.若在编码器中有50个编码对象,则要求输出二进制代码位数为B位。

A.5B.6C.10D.50

10.一个16选一的数据选择器,其地址输入(选择控制输入)端有C个。

A.1B.2C.4D.16

11.四选一数据选择器的数据输出Y与数据输入Xi和地址码Ai之间的逻辑表达式为Y=A。

A.B.C.D.

12.一个8选一数据选择器的数据输入端有E个。

A.1B.2C.3D.4E.8

13.在下列逻辑电路中,不是组合逻辑电路的有D。

A.译码器B.编码器C.全加器D.寄存器

14.八路数据分配器,其地址输入端有C个。

15.用四选一数据选择器实现函数Y=,应使A。

A.D0=D2=0,D1=D3=1B.D0=D2=1,D1=D3=0

C.D0=D1=0,D2=D3=1D.D0=D1=1,D2=D3=0

16.N个触发器可以构成能寄存B位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N

17.在下列触发器中,有约束条件的是C。

A.主从JKF/FB.主从DF/FC.同步RSF/F(时钟脉冲)

D.边沿DF/F

18.一个触发器可记录一位二进制代码,它有C个稳态。

A.0B.1C.2D.3E.4

19.存储8位二进制信息要D个触发器。

A.2B.3C.4D.8

20.对于D触发器,欲使Qn+1=Qn,应使输入D=C。

A.0B.1C.QD.

21.对于JK触发器,若J=K,则可完成C触发器的逻辑功能。

A.RSB.DC.TD.Tˊ

22.欲使D触发器按Qn+1=n工作,应使输入D=D。

A.0B.1C.QD.

23.下列触发器中,没有约束条件的是BD。

A.基本RS触发器B.主从RS触发器C.同步R

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 逻辑 期末 复习题

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls

水资源可供水量与供需平衡分析PPT推荐.ppt

水资源可供水量与供需平衡分析PPT推荐.ppt