哈工大计算机组成原理试卷1及答案Word文档格式.doc

哈工大计算机组成原理试卷1及答案Word文档格式.doc

- 文档编号:12929665

- 上传时间:2022-09-30

- 格式:DOC

- 页数:10

- 大小:1,010.50KB

哈工大计算机组成原理试卷1及答案Word文档格式.doc

《哈工大计算机组成原理试卷1及答案Word文档格式.doc》由会员分享,可在线阅读,更多相关《哈工大计算机组成原理试卷1及答案Word文档格式.doc(10页珍藏版)》请在冰豆网上搜索。

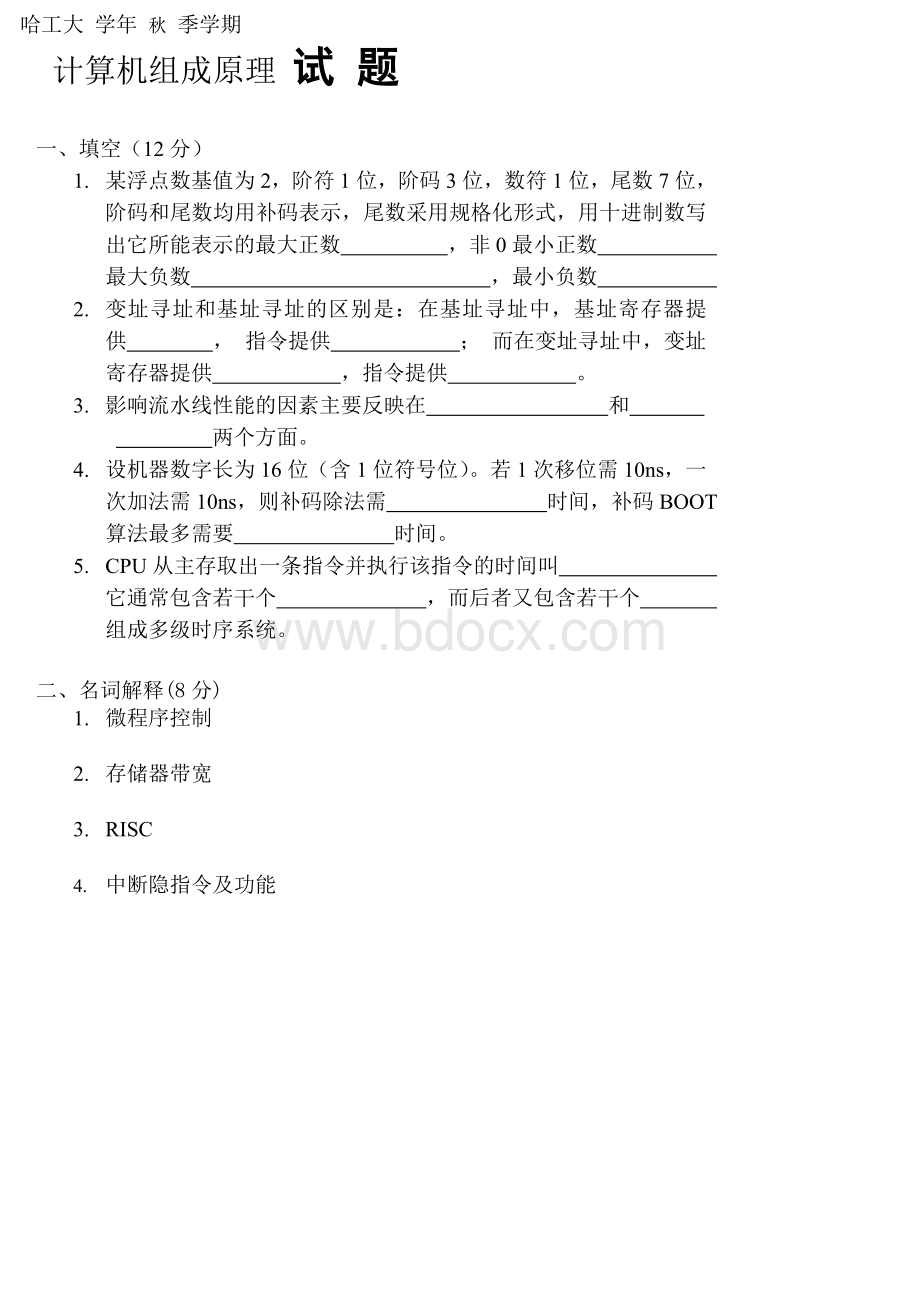

2.设主存容量为1MB,Cache容量为16KB,每字块有16个字,每字32位。

(1)若Cache采用直接相联映像,求出主存地址字段中各段的位数。

(2)若Cache采用四路组相联映像,求出主存地址字段中各段的位数。

3.某机有五个中断源,按中断响应的优先顺序由高到低为L0,L1,L2,L3,L4,现要求优先顺序改为L3,L2,L4,L0,L1,写出各中断源的屏蔽字。

中断源

屏蔽字

01234

L0

L1

L2

L3

L4

4.某机主存容量为4M×

16位,且存储字长等于指令字长,若该机的指令系统具备120种操作。

操作码位数固定,且具有直接、间接、立即、相对四种寻址方式。

(1)画出一地址指令格式并指出各字段的作用;

(2)该指令直接寻址的最大范围;

(3)一次间址的寻址范围;

(4)相对寻址的寻址范围。

四、(6分)

设阶码取3位,尾数取6位(均不包括符号位),按浮点补码运算规则

计算 [25]+[24]

五、画出DMA方式接口电路的基本组成框图,并说明其工作过程(以输入设备为例)。

(8分)

六、(10分)设CPU共有16根地址线,8根数据线,并用作访存控制信号,用作读写控制信号,现有下列存储芯片:

RAM:

1K×

8位、2K×

4位、4K×

8位

ROM:

2K×

8位、4K×

以及74138译码器和各种门电路(自定),画出CPU与存储器连接图。

要求:

(1)最大4K地址空间为系统程序区,与其相邻2K地址空间为用户

程序区。

(2)合理选用上述存储芯片,说明各选几片?

写出每片存储芯片的地址范围。

(3)详细画出存储芯片的片选逻辑。

允许输出

允许写

74138

七、假设CPU在中断周期用堆栈保存程序断点,且进栈时栈指针减一,出栈时栈指针加一。

试写出中断返回指令(中断服务程序的最后一条指令),在取指阶段和执行阶段所需的全部微操作命令及节拍安排。

若采用微程序控制,则还需要增加哪些微操作。

(10分)

八、除了采用高速芯片外,从计算机的各个子系统的角度分析,指出6种以上提高整机速度的措施。

计算机组成原理试题答案

1.127;

1/512;

-1/512-1/32768;

-128。

2.基地址;

形式地址;

基地址;

形式地址。

3.访存冲突;

相关问题。

4.300ns;

310ns。

5.指令周期;

机器周期;

节拍。

1.微程序控制

答:

采用与存储程序类似的方法来解决微操作命令序列的形成,将一条机器指令编写成一个微程序,每一个微程序包含若干条微指令,每一条指令包含一个或多个微操作命令。

2.存储器带宽

每秒从存储器进出信息的最大数量,单位可以用字/秒或字节/秒或位/秒来表示。

3.RISC

RISC是精简指令系统计算机,通过有限的指令条数简化处理器设计,已达到提高系统执行速度的目的。

4.中断隐指令及功能

中断隐指令是在机器指令系统中没有的指令,它是CPU在中断周期内由硬件自动完成的一条指令,其功能包括保护程序断点、寻找中断服务程序的入口地址、关中断等功能。

1.答:

总线在完成一次传输周期时,可分为四个阶段:

·

申请分配阶段:

由需要使用总线的主模块(或主设备)提出申请,经总线仲裁机构决定下一传输周期的总线使用权授于某一申请者;

寻址阶段:

取得了使用权的主模块,通过总线发出本次打算访问的从模块(或从设备)的存储地址或设备地址及有关命令,启动参与本次传输的从模块;

传数阶段:

主模块和从模块进行数据交换,数据由源模块发出经数据总线流入目的模块;

结束阶段:

主模块的有关信息均从系统总线上撤除,让出总线使用权。

2.答:

(1)若Cache采用直接相联映像:

字块中含64个字节,字块的位数为b=6。

Cache中含有256个字块,所以字块地址位数c=8。

主存容量为1M字节,总位数为20。

主存字块标记位数t=6。

(2)若Cache采用四路组相联映像,

每组含有四个字块,每组含256个字节。

Cache中含有64个字块,所以组地址位数q=6。

主存字块标记位数t=8。

3.答:

设屏蔽位为“1”时表示对应的中断源被屏蔽,屏蔽字排列如下:

01000

00000

11001

11101

11000

4.答:

(1)指令字长16位,操作码为7位,寻址特征位2位,地址码7位;

(2)-64~63;

(3)216;

(4)216.

被加数为 0,101;

0.100100,[x]补=00,101;

00.100100

加数为 0,100;

1.010100,[y]补=00,100;

11.010100

(1)对阶:

[△j]补=[jx]补-[jy]补=00,101+11,100=00,001

即△j=1,则y的尾数向右移一位,阶码相应加1,即

[y]’补=00,101;

11.101010

②求和

+=+[Sy]补

=00.100100+11.101010

=00.001110

即 [x+y]补=00,101;

00.001110

尾数出现“00.0”,需左规。

③规格化

左规后得[x+y]补=00,011;

00.111000

∴[x+y]补=00,111;

五、(8分)

DMA方式接口电路的基本组成框图如下:

以数据输入为例,具体操作如下:

①从设备读入一个字到DMA的数据缓冲寄存器BR中,表示数据缓冲寄存器“满”(如果I/O设备是面向字符的,则一次读入一个字节,组装成一个字);

②设备向DMA接口发请求(DREQ);

③DMA接口向CPU申请总线控制权(HRQ);

④CPU发回HLDA信号,表示允许将总线控制权交给DMA接口;

⑤将DMA主存地址寄存器中的主存地址送地址总线;

⑥通知设备已被授予一个DMA周期(DACK),并为交换下一个字做准备;

⑦将DMA数据缓冲寄存器的内容送数据总线;

⑧命令存储器作写操作;

⑨修改主存地址和字计数值;

⑩判断数据块是否传送结束,若未结束,则继续传送;

若己结束,(字计数器溢出),则向CPU申请程序中断,标志数据块传送结束。

六、(10分)

方法一:

地址空间描述如下:

ROM对应的空间:

1111 1111 1111 1111

1111 0000 0000 0000

RAM对应的空间:

1110 1111 1111 1111

1110 1000 0000 0000

选择ROM芯片为2K×

8位的两片,RAM芯片为2K×

4位的两片

ROM芯片1:

1111 1000 0000 0000

ROM芯片2:

1111 0111 1111 1111

RAM芯片1、2:

(位扩展)

CPU与存储器连接图见下页:

方法二:

选择ROM芯片为4K×

8位的一片,RAM芯片为2K×

七、(10分)

组合逻辑设计的微操作命令:

取指:

T0:

PC→MAR

T1:

M[MAR]→MDR,PC+1→PC

T2:

MDR→IR,OP[IR]→微操作形成部件

执行:

SP→MAR

M[MAR]→MDR

MDR→PC,SP+1→SP

微程序设计的微操作命令:

取指微程序:

Ad[CMIR]→CMAR

T3:

T4:

T5:

OP[IR]→CMAR

中断返回微程序:

八、(8分)

针对存储器,可以采用Cache-主存层次的设计和管理提高整机的速度;

针对存储器,可以采用主存-辅存

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 哈工大 计算机 组成 原理 试卷 答案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

国企会计岗位笔试试题及答案解析(分享).docx

国企会计岗位笔试试题及答案解析(分享).docx

行政事业单位内部审计流程图(按照新内部审计准则).xls

行政事业单位内部审计流程图(按照新内部审计准则).xls

毛概实现伟大中国梦优质PPT.pptx

毛概实现伟大中国梦优质PPT.pptx