计算机组成原理课程设计报告乘法除法子函数编程思想.docx

计算机组成原理课程设计报告乘法除法子函数编程思想.docx

- 文档编号:12854102

- 上传时间:2023-04-22

- 格式:DOCX

- 页数:28

- 大小:240.97KB

计算机组成原理课程设计报告乘法除法子函数编程思想.docx

《计算机组成原理课程设计报告乘法除法子函数编程思想.docx》由会员分享,可在线阅读,更多相关《计算机组成原理课程设计报告乘法除法子函数编程思想.docx(28页珍藏版)》请在冰豆网上搜索。

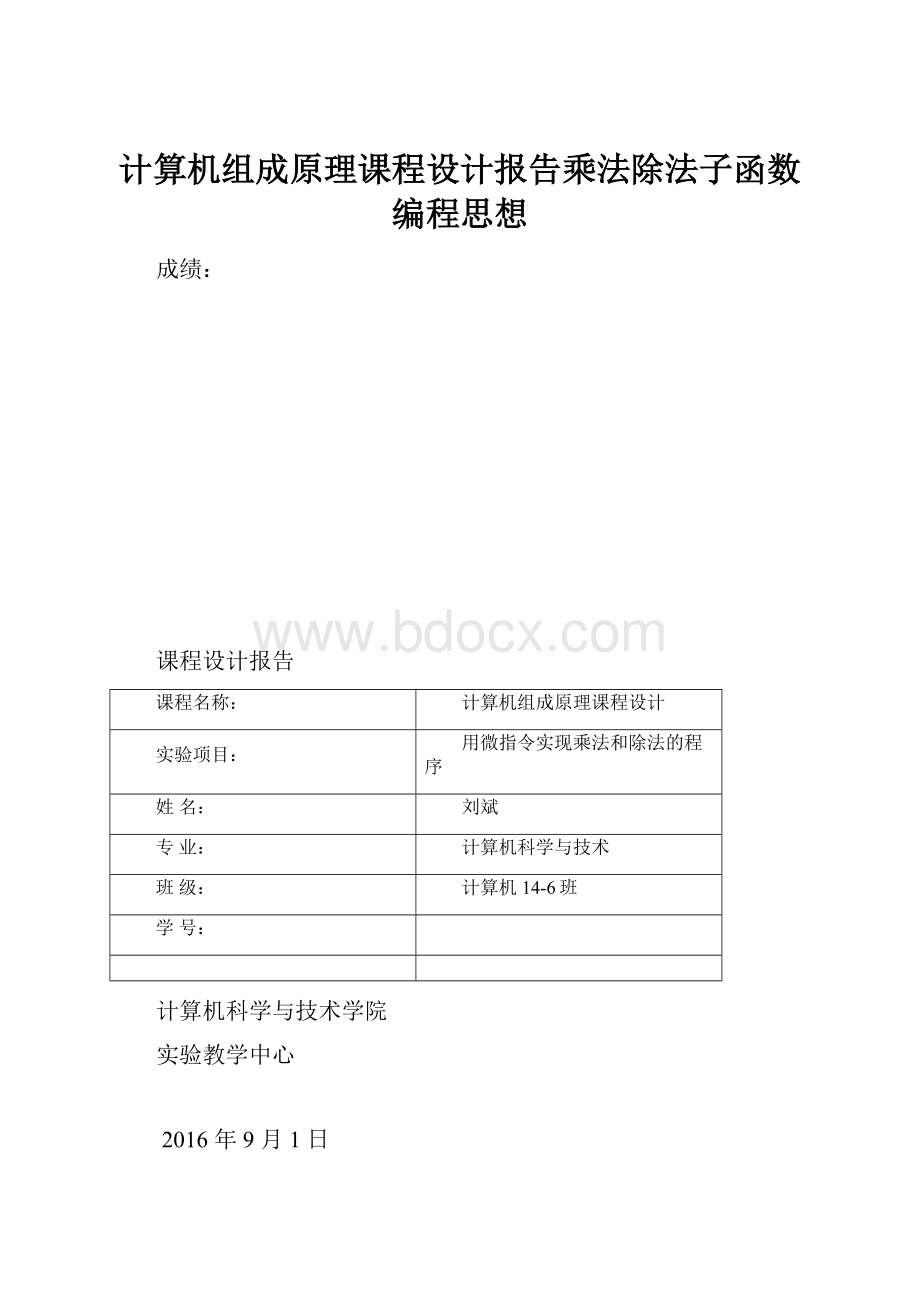

计算机组成原理课程设计报告乘法除法子函数编程思想

成绩:

课程设计报告

课程名称:

计算机组成原理课程设计

实验项目:

用微指令实现乘法和除法的程序

姓名:

刘斌

专业:

计算机科学与技术

班级:

计算机14-6班

学号:

计算机科学与技术学院

实验教学中心

2016年9月1日

设计项目名称:

用微指令实现乘法和除法的程序(2学时)

一.设计目的

1.在实验机上设计实现机器指令及对应的微指令(微程序)并验证,从而进一步掌握微程序设计控制器的基本方法并了解指令系统与硬件结构的对应关系;

2.通过控制器的微程序设计,综合理解计算机组成原理课程的核心知识并进一步建立整机系统的概念;

3.培养综合实践及独立分析、解决问题的能力。

二.设计内容

针对COP2000实验仪,从详细了解该模型机的指令/微指令系统入手,以实现乘法和除法运算功能为应用目标,在COP2000的集成开发环境下,设计全新的指令系统并编写对应的微程序;之后编写实现乘法和除法的程序进行设计的验证。

三.使用仪器

1.硬件

COP2000实验仪

PC机

2.软件

COP2000仿真软件

3.辅助

COP2000计算机组成原理实验仪说明书。

四.设计步骤

1.知识储备

1.1.掌握计算机组成原理相关知识

1.2.掌握COP2000模型机的微程序控制器原理。

1.3.掌握有关计算机中实现乘法和除法的算法流程与相应的硬件实现原理。

2.熟悉实验环境

2.1.熟悉COP2000仿真软件

2.2.将1.3中算法与COP2000实验仪的硬件资源相对应

3.分步设计指令系统并逐步验证

3.1.设计“数据移动”相关指令,并写程序验证功能

3.2.设计“加减法”相关指令,并写程序验证功能

3.3.设计“整数移位”相关指令,并写程序验证功能

3.4.设计“跳转”相关指令,并写程序验证功能

3.5.设计“调用子函数”相关指令,并写程序验证功能

4.设计乘除法,同时验证指令系统的整体功能

4.1.乘法算法设计,并用全新的指令系统实现,验证程序正确性的同时验证指令系统的正确性。

4.2.除法算法设计,并用全新的指令系统实现,验证程序正确性的同时验证指令系统的正确性。

五.微程序设计指令原理

该模型机指令系统的特点:

1.总体概述

COP2000模型机包括了一个标准CPU所具备所有部件,这些部件包括:

运算器ALU、累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。

其中运算器和中断控制电路以及跳转控制电路用CPLD来实现,其它电路都是用离散的数字电路组成。

微程序控制部分也可以用组合逻辑控制来代替。

模型机为8位机,数据总线、地址总线都为8位,但其工作原理与16位机相同。

相比而言8位机实验减少了烦琐的连线,但其原理却更容易被学生理解、吸收。

模型机的指令码为8位,根据指令类型的不同,可以有0到2个操作数。

指令码的最低两位用来选择R0-R3寄存器,在微程序控制方式中,用指令码做为微地址来寻址微程序存储器,找到执行该指令的微程序。

而在组合逻辑控制方式中,按时序用指令码产生相应的控制位。

在本模型机中,一条指令最多分四个状态周期,一个状态周期为一个时钟脉冲,每个状态周期产生不同的控制逻辑,实现模型机的各种功能。

模型机有24位控制位以控制寄存器的输入、输出,选择运算器的运算功能,存储器的读写。

模型机的缺省的指令集分几大类:

算术运算指令、逻辑运算指令、移位指令、数据传输指令、跳转指令、中断返回指令、输入/输出指令。

2.模型机的寻址方式

表1模型机的寻址方式

模型机的寻址方式

寻址方式说明

指令举例

指令说明

累加器寻址

操作数为累加器A

CPLA

将累加器A的值取反

隐含寻址累加器A

OUT

将累加器A的值输出到输出端口寄存器OUT

寄存器寻址

参与运算的数据在R0~R3的寄存器中

ADDA,R0

将寄存器R0的值加上累加器A的值,再存入累加器A中

寄存器间接寻址

参与运算的数据在存储器EM中,数据的地址在寄存器R0-R3中

MOVA,@R1

将寄存器R1的值作为地址,把存储器EM中该地址的内容送入累加器A中

存储器直接寻址

参与运算的数据在存储器EM中,数据的地址为指令的操作数。

ANDA,40H

将存储器EM中40H单元的数据与累加器A的值作逻辑与运算,结果存入累加器A

立即数寻址

参与运算的数据为指令的操作数。

SUBA,#10H

从累加器A中减去立即数10H,结果存入累加器A

该模型机微指令系统的特点(包括其微指令格式的说明等):

该模型机的微命令是以直接表示法进行编码的,其特点是操作控制字段中的每一位代表一个微命令。

这种方法的优点是简单直观,其输出直接用于控制。

缺点是微指令字较长,因而使控制存储器容量较大。

3.微指令格式的说明

模型机有24位控制位以控制寄存器的输入、输出,选择运算器的运算功能,存储器的读写。

微程序控制器由微程序给出24位控制信号,而微程序的地址又是由指令码提供的,也就是说24位控制信号是由指令码确定的。

该模型机的微指令的长度为24位,其中微指令中只含有微命令字段,没有微地址字段。

其中微命令字段采用直接按位的表示法,哪位为0,表示选中该微操作,而微程序的地址则由指令码指定。

这24位操作控制信号的功能如表2所示:

(按控制信号从左到右的顺序依次说明)

表2微指令控制信号的功能

操作控制信号

控制信号的说明

XRD

外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

EMWR

程序存储器EM写信号。

EMRD

程序存储器EM读信号。

PCOE

将程序计数器PC的值送到地址总线ABUS上。

EMEN

将程序存储器EM与数据总线DBUS接通,由EMWR和EMRD决定是将DBUS数据写到EM中,还是从EM读出数据送到DBUS。

IREN

将程序存储器EM读出的数据打入指令寄存器IR和微指令计数器μPC。

EINT

中断返回时清除中断响应和中断请求标志,便于下次中断。

ELP

PC打入允许,与指令寄存器的IR3、IR2位结合,控制程序跳转。

MAREN

将数据总线DBUS上数据打入地址寄存器MAR。

MAROE

将地址寄存器MAR的值送到地址总线ABUS上。

OUTEN

将数据总线DBUS上数据送到输出端口寄存器OUT里。

STEN

将数据总线DBUS上数据存入堆栈寄存器ST中。

RRD

读寄存器组R0~R3,寄存器R?

的选择由指令的最低两位决定。

RWR

写寄存器组R0~R3,寄存器R?

的选择由指令的最低两位决定。

CN

决定运算器是否带进位移位,CN=1带进位,CN=0不带进位。

FEN

将标志位存入ALU内部的标志寄存器。

X2

X2、X1、X0三位组合来译码选择将数据送到DBUS上的寄存器。

X1

X0

WEN

将数据总线DBUS的值打入工作寄存器W中。

AEN

将数据总线DBUS的值打入累加器A中。

S2

S2、S1、S0三位组合决定ALU做何种运算。

S1

S0

COP2000中有7个寄存器可以向数据总线输出数据,但在某一特定时刻只能有一个寄存器输出数据.由X2,X1,X0决定那一个寄存器输出数据。

X2X1X0

输出寄存器

000

IN_OE外部输入门

001

IA_OE中断向量

010

ST_OE堆栈寄存器

011

PC_OEPC寄存器

100

D_OE直通门

101

R_OE右移门

110

L_OE左移门

111

没有输出

COP2000中的运算器由一片EPLD实现.有8种运算,通过S2,S1,S0来选择。

运算数据由寄存器A及寄存器W给出,运算结果输出到直通门D。

S2S1S0

功能

000

A+W加

001

A-W减

010

A|W或

011

A&W与

100

A+W+C带进位加

101

A-W-C带进位减

110

~AA取反

111

A输出A

六.设计具体过程

由于一次性设计整个指令系统比较困难,这里将指令系统分为五大部分,每个部分独立设计并进行模块验证。

分别是,数据移动指令,加减法指令,位移指令,跳转指令,子函数指令。

第一部分:

数据移动指令

NMOVA,R?

NMOVA,MM

NMOVA,#II

NMOVR?

A

NMOVMM.A

NMOVR?

#II

编写验证程序:

NMOVA,#011H

NMOVR0,A

NMOVA,#022H

NMOVR1,#033H

NMOVA,R0

NMOV0E1H,A

NMOVA,#022H

NMOVA,0E1H

分步执行程序,直至每步结果正确。

通过观察每步操作,以证明结果正确,可进行下一部分设计。

第二部分:

加减法指令设计

NADDA,R?

NADDA,MM

NADDA,#II

NSUBA,R?

NSUBA,MM

NSUBA,#II

编写验证程序:

NMOVA,#011H

NMOVR0,#02H

NMOV0E1H,A

NADDA,#01H

NADDA,R0

NADDA,0E1H

NSUBA,#01H

NSUBA,R0

NSUBA,0E1H

分步执行程序,直至每步结果正确。

通过观察每步操作,以证明结果正确,可进行下一部分设计。

第三部分:

位移指令

NRRCA

编写验证程序:

NMOVA,#0FFH

NRRCA

分步执行程序,直至每步结果正确。

通过观察每步操作,以证明结果正确,可进行下一部分设计。

第四部分:

跳转指令

NJC

NJZ

NJMP

编写验证程序:

NMOVA,#0FFH

NSUBA,#0FFH

NJZNEXT

NMOVA,#0DDH

NEXT:

NMOVA,#0FDH

NADDA,#0FDH

NJCNEXT2

NMOVA,#0EEH

NEXT2:

NJMPNEXT3

NMOVA,#0DDH

NEXT3:

NMOVA,#01H

分步执行程序,直至每步结果正确。

通过观察每步操作,以证明结果正确,可进行下一部分设计。

第五部分:

子函数指令

NCALLMM

NRET

编写验证程序:

NJMPNEXT

UP:

NMOVA,#02H

NRET

NEXT:

NCALLUP

NMOVA,#03H

分步执行程序,直至每步结果正确。

通过观察每步操作,以证明结果正确,可进行下一部分设计。

现在进行乘除法程序设计,并最终验证程序,同时验证指令系统

乘法程序设计:

NJMPMAIN

N_cheng_R0123:

NMOVR2,#0H

NMOVR3,#8H

NMOVA,#0H

N_cheng_loop:

NMOVA,R1

NRRCA

NJCN_cheng_jc_else

NJMPN_cheng_jc_end

N_cheng_jc_else:

NMOVA,R2

NADDA,R0

NMOVR2,A

N_cheng_jc_end:

NMOVA,R2

NRRCA

NMOVR2,A

NMOVA,R1

NRRCA

NMOVR1,A

NMOVA,R3

NSUBA,#1H

NJZN_cheng_ret

NMOVR3,A

NJMPN_cheng_loop

N_cheng_ret:

NMOVA,#0H

NRET

MAIN:

NMOVR0,#012H

NMOVR1,#011H

NCALLN_cheng_R0123

NMOVA,R1

NMOV0E1H,A

NMOVA,R2

NMOV0E0H,A

END

结果:

答案在E0,E1

除法程序设计:

NJMPMAIN

N_chu_R012:

NMOVR2,#0H

NMOVA,#0H

NADDA,R1

NJZN_chu_ret

N_chu_loop:

NMOVA,R0

NSUBA,R1

NJCN_chu_ret

NMOVR0,A

NMOVA,R2

NADDA,#01H

NMOVR2,A

NJMPN_chu_loop

N_chu_ret:

NRET

MAIN:

NMOVR0,#11H

NMOVR1,#2H

NCALLN_chu_R012

NMOVA,R0

NMOV0F0H,A

NMOVA,R2

NMOV0F1H,A

END

结果:

答案在F0,F1,F0为余数,F1为结果

子函数写入同一个程序进行测试:

编写程序:

NJMPMAIN

N_cheng_R0123:

NMOVR2,#0H

NMOVR3,#8H

NMOVA,#0H

N_cheng_loop:

NMOVA,R1

NRRCA

NJCN_cheng_jc_else

NJMPN_cheng_jc_end

N_cheng_jc_else:

NMOVA,R2

NADDA,R0

NMOVR2,A

N_cheng_jc_end:

NMOVA,R2

NRRCA

NMOVR2,A

NMOVA,R1

NRRCA

NMOVR1,A

NMOVA,R3

NSUBA,#1H

NJZN_cheng_ret

NMOVR3,A

NJMPN_cheng_loop

N_cheng_ret:

NMOVA,#0H

NRET

N_chu_R012:

NMOVR2,#0H

NMOVA,#0H

NADDA,R1

NJZN_chu_ret

N_chu_loop:

NMOVA,R0

NSUBA,R1

NJCN_chu_ret

NMOVR0,A

NMOVA,R2

NADDA,#01H

NMOVR2,A

NJMPN_chu_loop

N_chu_ret:

NRET

MAIN:

NMOVR0,#14H

NMOVR1,#11H

NCALLN_cheng_R0123

NMOVA,R1

NMOV0E1H,A

NMOVA,R2

NMOV0E0H,A

NMOVR0,#11H

NMOVR1,#2H

NCALLN_chu_R012

NMOVA,R0

NMOV0F0H,A

NMOVA,R2

NMOV0F1H,A

END

乘除连算运行结果

乘法结果在E0,E1,除法结果在F0,F1,F0为余数,F1为结果

至此,验证的,程序验证结果正确,微指令系统正确可用

七.运行结果

乘法结果

除法结果

乘除连算结果

八.程序代码

1.源程序代码

NJMPMAIN

N_cheng_R0123:

NMOVR2,#0H

NMOVR3,#8H

NMOVA,#0H

N_cheng_loop:

NMOVA,R1

NRRCA

NJCN_cheng_jc_else

NJMPN_cheng_jc_end

N_cheng_jc_else:

NMOVA,R2

NADDA,R0

NMOVR2,A

N_cheng_jc_end:

NMOVA,R2

NRRCA

NMOVR2,A

NMOVA,R1

NRRCA

NMOVR1,A

NMOVA,R3

NSUBA,#1H

NJZN_cheng_ret

NMOVR3,A

NJMPN_cheng_loop

N_cheng_ret:

NMOVA,#0H

NRET

N_chu_R012:

NMOVR2,#0H

NMOVA,#0H

NADDA,R1

NJZN_chu_ret

N_chu_loop:

NMOVA,R0

NSUBA,R1

NJCN_chu_ret

NMOVR0,A

NMOVA,R2

NADDA,#01H

NMOVR2,A

NJMPN_chu_loop

N_chu_ret:

NRET

MAIN:

NMOVR0,#14H

NMOVR1,#11H

NCALLN_cheng_R0123

NMOVA,R1

NMOV0E1H,A

NMOVA,R2

NMOV0E0H,A

NMOVR0,#11H

NMOVR1,#2H

NCALLN_chu_R012

NMOVA,R0

NMOV0F0H,A

NMOVA,R2

NMOV0F1H,A

END

2.微指令系统指令系统表

第一部分,数据移动指令

第二部分,加减指令

第三部分,位移指令

第四部分,跳转指令

第五部分,子函数调用指令

九.设计总结

本次指令系统设计特点:

指令系统设计时,采用分步完成的方式,极大的降低了设计的困难程度。

先将指令系统划分成六大部分:

数据移动,加减,位移,跳转,子函数。

然后对于每一部分都独立设计,一部分设计完就写个小程序验证正确性,避免了最后统一验证时错误过多难以解决的尴尬场面。

当我们每一个小部分都验证完成,那么我们整个系统也就设计完成。

优点:

简介有效,极大的降低设计的困难程度。

缺点:

多次验证需要设计的程序比较多。

整体来说,我们的优点明显好于缺点,所以此种设计方式非常有优势。

本次乘除法程序设计特点:

通过查找资料,明确了我们将使用的具体算法,然后在纸上画好程序框图,然后对照程序框图书写伪代码,再将伪代码翻译成对应指令系统的汇编语言。

经过程序框图梳理思路,然后又有伪代码的辅助,最后一步翻译就变得非常简单。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机 组成 原理 课程设计 报告 乘法 除法 子函数 编程 思想

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《搭船的鸟》教案.docx

《搭船的鸟》教案.docx