《数字电子技术》实验指导书.doc

《数字电子技术》实验指导书.doc

- 文档编号:1257222

- 上传时间:2022-10-19

- 格式:DOC

- 页数:99

- 大小:8.97MB

《数字电子技术》实验指导书.doc

《《数字电子技术》实验指导书.doc》由会员分享,可在线阅读,更多相关《《数字电子技术》实验指导书.doc(99页珍藏版)》请在冰豆网上搜索。

实验一门电路

本实验为验证性实验

一、实验目的

熟悉门电路的逻辑功能。

二、实验原理

TTL集成与非门是数字电路中广泛使用的一种基本逻辑门。

使用时,必须对它的逻辑功能、主要参数和特性曲线进行测试,以确定其性能的好坏。

与非门逻辑功能测试的基本方法是按真值表逐项进行。

但有时按真值表测试显得有些多余。

根椐与非门的逻辑功能可知,当输入端全为高电平时,输出是低电平;当有一个或几个输入端为低电平时,输出为高电平。

可以化简逻辑函数或进行逻辑变换。

三、实验内容及步骤

6

14Vcc

7地

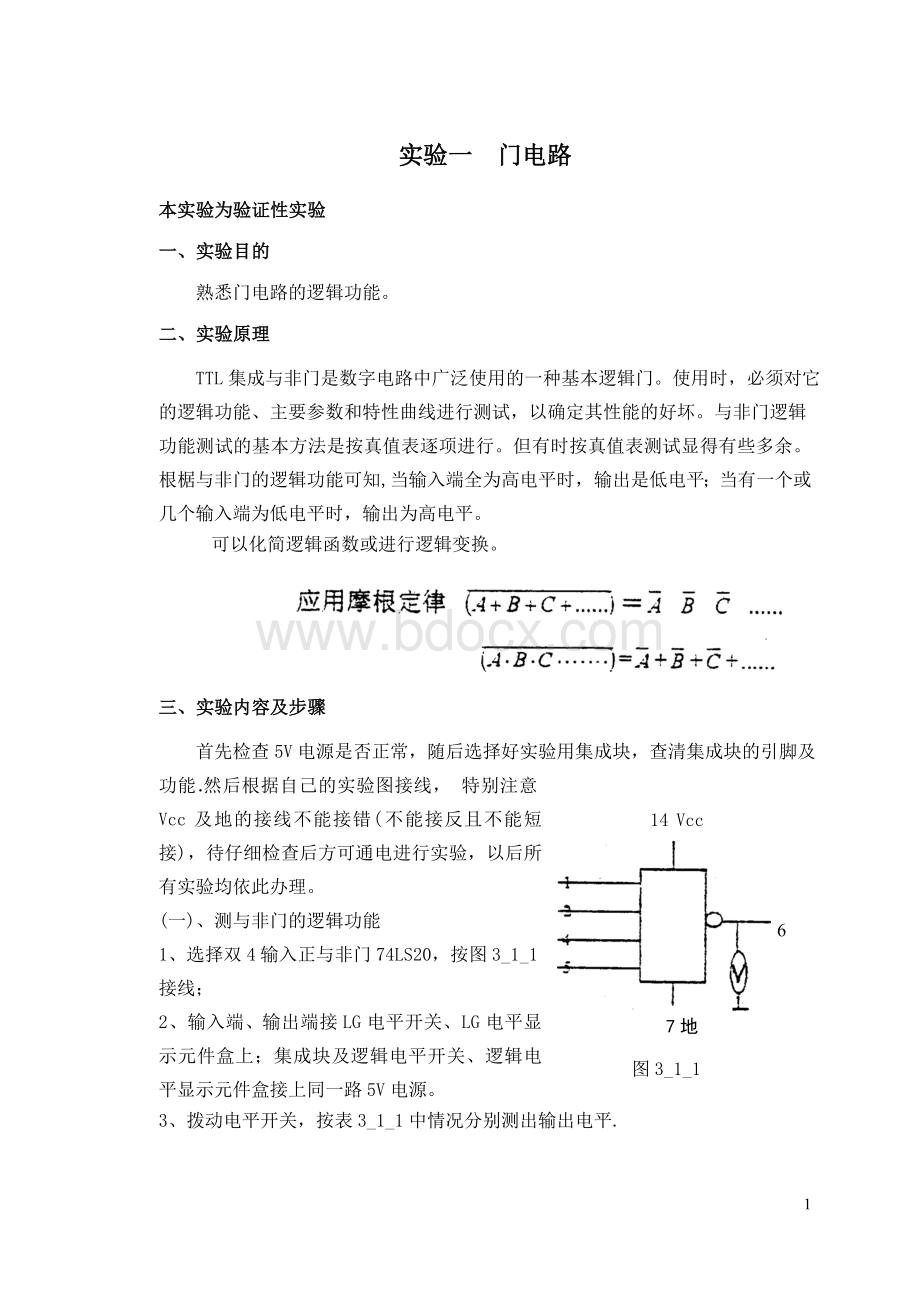

首先检查5V电源是否正常,随后选择好实验用集成块,查清集成块的引脚及功能.然后根据自己的实验图接线,特别注意Vcc及地的接线不能接错(不能接反且不能短接),待仔细检查后方可通电进行实验,以后所有实验均依此办理。

(一)、测与非门的逻辑功能

1、选择双4输入正与非门74LS20,按图3_1_1接线;

图3_1_1

2、输入端、输出端接LG电平开关、LG电平显示元件盒上;集成块及逻辑电平开关、逻辑电平显示元件盒接上同一路5V电源。

3、拨动电平开关,按表3_1_1中情况分别测出输出电平.

表3_1_1

输入端

输出端

1

2

4

5

6

电位(V)

逻辑状态

1

l

l

l

O

1

1

1

O

O

1

l

0

0

0

1

O

0

O

O

图3_1_2

(二)、测试与或非门的逻辑功能

l、选两路四输入与或非门电路1个74LS55,按图3_1_2接线:

2、输入端接电平的输出插口,拨动开关当输入端为下表情况时分别测试输出端(8)的电位,将结果填入表3_1_2中:

表3_1_2

输入端

输出端

1

2

3

4

10

11

12

13

8

电位

(V)

逻辑

状态

l

1

1

1

0

0

0

O

l

1

1

1

0

0

0

1

0

0

0

O

1

l

l

1

1

O

O

0

1

l

1

1

0

O

O

l

O

0

O

l

0

O

O

O

O

O

O

0

(三)、测逻辑电路的逻辑关系

用74LS00电路组成下列逻辑电路,按图3_1_3、图3_1_4接线,写出下列图的逻辑表达表并化简,将各种输入电压情况下的输出电压分别填入表3_1_3、表3_1_4中,验证化简的表达式。

图3_1_3

Z

表3_1_3

输入

输出

A

B

Z

0

O

O

1

l

O

1

1

图3_1_4

A

B

Z

表3_1_4

输入

输出

A

B

Z

0

O

O

1

l

O

1

1

(四)、观察与非门对脉冲的控制作用

选一块与非门74LS20按下面两组图3_1_5(a)、(b)接线,将一个输入端接连续脉冲用示波器观察两种电路的输出波形。

(a)

+5V(b)

图3_1_25

在做以上各个实验时,请特别注意集成块的插入位置与接线是否正确,每次必须在接线后经复核确定无误后方可通电实验,并要养成习惯。

四、实验仪器与器材

1、JD-2000通用电学实验台一台

2、CA8120A示波器一台

3、DT930FD数字多用表一块

4、主要器材74LS002片,74LS551片,74LS201片,逻辑开关盒1个

五、实验报告要求

整理实验数据,并对数据及波形进行一一分析,比较实验结果,分析“与非门”的逻辑功能并作讨论!

六:

注意事项:

l、接拆线都要在断开电源(5V)的情况下进行。

2、TTL电路电源电压Vcc=+5V;检查电源是否为5V(不要超过+5V)。

七、实验思考题

l、与非门什么情况下输出高电平?

什么情况下输出低电平?

与非门不用的输入端应如何处理?

2、与或非门在什么情况下输出高电平?

什么情况下输出低电平?

与或非门中不用的与门输入端应如何处理?

不用的与门应如何处理?

3、如果与非门的一个输入端接连续时钟脉冲,那么:

(1)其余输入端是什么状态时,允许脉冲通过?

脉冲通过时,输出端波形与输入端波形有何差别?

(2)其余输入端是什么状态时,不允许脉冲通过?

这种情况下与非门输出是什么状态?

实验二三态门和OC门的研究

本实验为验证性实验

一、实验目的

(1)熟悉两种特殊的门电路:

三态门和OC门;

(2)了解“总线”结构的工作原理。

二、实验原理

数字系统中,有时需把两个或两个以上集成逻辑门的输出端连接起来,完成一定的逻辑功能。

普通TTL门电路的输出端是不允许直接连接的。

图2_1示出了两个TTL门输出短接的情况,为简单起见,图中只画出了两个与非门的推拉式输出级。

设门A处于截止状态,若不短接,输出应为高电平;设门B处于导通状态,若不短接,输出应为低电平。

在把门A和门B的输出端作如图3_2_1所示连接后,从电源Vcc经门A中导通的T4、D3和门B中导通的T5到地,有了一条通路,其不良后果为:

图3_2_1不正常情况:

普通TTL门电路输出端短接

(1)输出电平既非高电平,也非低电平,而是两者之间的某一值,导致逻辑功能混乱。

(2)上述通路导致输出级电流远大于正常值(正常情况下T4和T5总有一个截止),导致功耗剧增,发热增大,可能烧坏器件。

集电极开路门和三态门是两种特殊的TTL电路,它们允许把输出端互相连在一起使用。

1.集电极开路门(OC门)

集电极开路门(Open-CollectorGate),简称OC门。

它可以看成是图3_2_1所示的TTL与非门输出级中移去了T4、D3部分。

集电极开路与非门的电路结构与逻辑符号如图3_2_2所示。

必须指出:

OC门只有在外接负载电阻Rc和电源Ec后才能正常工作,如图中虚线所示。

(a)电路结构

(b)国标逻辑符号

(c)惯用逻辑符号

图3_2_2集电极开路与非门

由两个集电极开路与非门(0C)输出端相连组成的电路如图3_2_3所示,它们的输出:

即把两个集电极开路与非门的输出相与(称为线与),完成与或非的逻辑功能。

0C门主要有以下三方面的应用:

(1)实现电平转换

图3_2_3OC门的线与应用

无论是用TTL电路驱动CMOS电路还是用CMOS电路驱动TTL电路,驱动门必须能为负载门提供合乎标准的高、低电平和足够的驱动电流,即必须同时满足下列四式:

驱动门负载门

VOH(min)≥VIH(min)

VOL(max)≤VIL(max)

IOH(max)≥IIH

IOL(max)≥IIL

其中:

VOH(min)--门电路输出高电平VOH的下限值;

VOL(max)--门电路输出低电平VOL的上限值;

IOH(max)--门电路带拉电流负载的能力,或称放电流能力;

IOL(max)—门电路带灌电流负载的能力,或称吸电流能力;

VIH(min)--为能保证电路处于导通状态的最小输入(高)电平;

VIL(max)--为能保证电路处于截止状态的最大输入(低)电平。

IIH—输入高电平时流入输入端的电流;

IIL--输入低电平时流出输入端的电流。

当74系列或74LS系列TTL电路驱动CD4000系列或74HC系列CMOS电路时,不能直接驱动,因为74系列的TTL电路VOH(min)=2.4V,74LS系列的TTL电路VOH(min)=2.7V,CD4000系列的CMOS电路VIH(min)=3.5V,74HC系列CMOS电路VIH(min)=3.15V,显然不满足VOH(min)≥VIH(min)

最简单的解决方法是在TTL电路的输出端与电源之间接入上拉电阻Rc,如图3_2_4所示。

图3_2_4TTL(OC)门驱动CMOS电路的电平转换

(2)实现多路信号采集,使两路以上的信息共用一个传输通道(总线);

(3)利用电路的线与特性方便地完成某些特定的逻辑功能。

在实际应用时,有时需将几个OC门的输出端短接,后面接m个普通TTL与非门作为负载,如图3_2_5所示。

为保证集电极开路门的输出电平符合逻辑要求,Rc的数值选择范围为:

m'(7)个输入端

(a)计算Rc最大值

(b)计算Rc最小值

图3_2_5计算OC门外接电阻Rc的工作状态

其中IcEO--OC门输出三极管T5截止时的漏电流;

Ec—外接电源电压值;

m--TTL负载门个数;

n—输出短接的OC门个数;

m’—各负载门接到OC门输出端的输入端总和。

Rc值的大小会影响输出波形的边沿时间,在工作速度较高时,Rc的取值应接近Rc(min)。

2.三态门

三态门,简称TSL(Three-stateLogic)门,是在普通门电路的基础上,附加使能控制端和控制电路构成的。

图3_2_6所示为三态门的结构和逻辑符号。

三态门除了通常的高电平和低电平两种输出状态外,还有第三种输出状态——高阻态。

处于高阻态时,电路与负载之间相当于开路。

图(a)是使能端高电平有效的三态与非门,当使能端EN=1时,电路为正常的工作状态,与普通的与非门一样,实现y=;当EN=0时,为禁止工作状态,y输出呈高阻状态。

图(b)是使能端低电平有效的三态与非门,当=0时,电路为正常的工作状态,实现Y=;当=1时,电路为禁止工作状态,Y输出呈高阻状态。

(a)单向总线方式

(b)双向总线方式

图3_2_7三态门总线传输方式

(a)使能控制端高电平有效

(b)使能控制端低电平有效

图3_2_6三态门的结构和逻辑符号

三态门电路用途之一是实现总线传输。

总线传输的方式有两种,一种是单向总线,如图3_2_7(a)所示,功能表见表3_2_1所示,可实现信号A1、A2、A3向总线Y的分时传送;另一种是双向总线,如图3_2_7(b)所示,功能表见表3_2_2所示,可实现信号的分时双向传送。

单向总线方式下,要求只有需要传输信息的那个三态门的控制端处于使能状态(EN=1),其余各门皆处于禁止状态(EN=O),否则会出现与普通TTL门线与运用时同样的问题,因而是绝对不允许的。

9

表3_2_1单向总线逻辑功能

表3_2_2双向总线逻辑功能

三、预习要求

(1)根据设计任务的要求,画出逻辑电路图,并注明管脚号。

(2)拟出记录测量结果的表格。

(3)完成第七项中的思考题1、2、3。

四、实验内容

图3_2_8设计要求框图

1、用三态门实现三路信号分时传送的总线结构。

框图如图3_2_8所示,功能如表3_2_3所示。

表3_2_3设计要求的逻辑功能

在实验中要求:

(1)静态验证控制输入和数据输入端加高、低电平,用电压表测量输出高电平、低电平的电压值。

(2)动态验证控制输入加高、低电平,数据输入加连续矩形脉冲,用示波器对应地观察数据输入波形和输出波形。

(3)动态验证时,分别用示波器中的AC耦合与DC耦合,测定输出波形的幅值Vp _p

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电子技术 数字 电子技术 实验 指导书

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls