MCS-51单片机复习要点.doc

MCS-51单片机复习要点.doc

- 文档编号:1256718

- 上传时间:2022-10-19

- 格式:DOC

- 页数:31

- 大小:348KB

MCS-51单片机复习要点.doc

《MCS-51单片机复习要点.doc》由会员分享,可在线阅读,更多相关《MCS-51单片机复习要点.doc(31页珍藏版)》请在冰豆网上搜索。

MCS-51单片机

8051单片机是8位单片机,有40个管脚,8根数据线,16根地址线。

单片机的八大组成部分:

CPU、ROM、RAM、I/O、定时/计数器、串口、SFR、中断服务系统

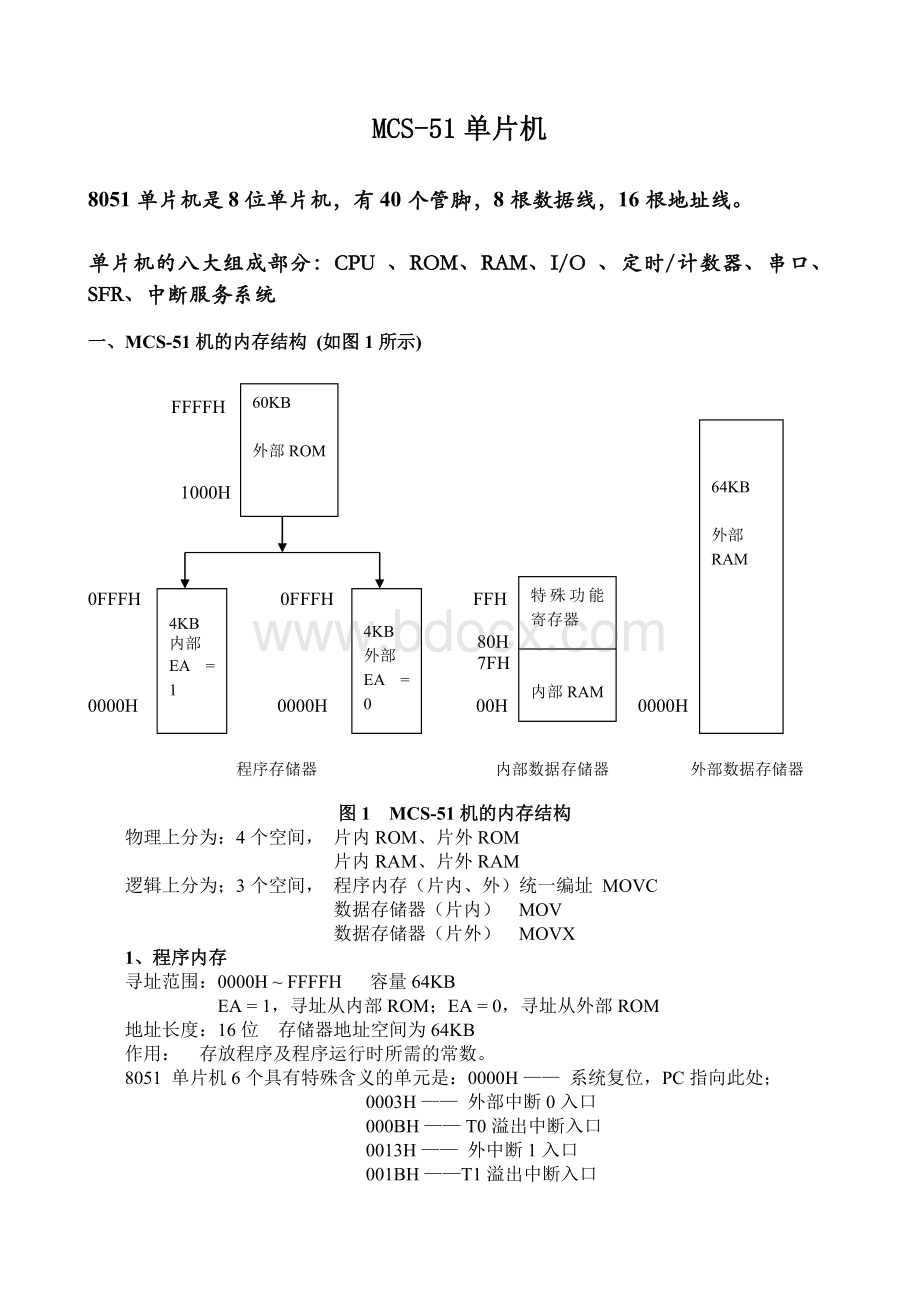

一、MCS-51机的内存结构(如图1所示)

60KB

外部ROM

64KB

外部

RAM

4KB

内部

EA=1

4KB

外部

EA=0

特殊功能寄存器

内部RAM

FFFFH

FFFFH

1000H

0FFFH0FFFHFFH

80H

7FH

0000H0000H00H0000H

7F

程序存储器内部数据存储器外部数据存储器

图1MCS-51机的内存结构

物理上分为:

4个空间,片内ROM、片外ROM

片内RAM、片外RAM

逻辑上分为;3个空间,程序内存(片内、外)统一编址MOVC

数据存储器(片内)MOV

数据存储器(片外)MOVX

1、程序内存

寻址范围:

0000H~FFFFH容量64KB

EA=1,寻址从内部ROM;EA=0,寻址从外部ROM

地址长度:

16位存储器地址空间为64KB

作用:

存放程序及程序运行时所需的常数。

8051单片机6个具有特殊含义的单元是:

0000H——系统复位,PC指向此处;

0003H——外部中断0入口

000BH——T0溢出中断入口

0013H——外中断1入口

001BH——T1溢出中断入口

0023H——串口中断入口

2、内部数据存储器

物理上分为两大区:

00H~7FH即128B内RAM和SFR区。

如图2所示。

7FH

资料缓冲区

堆栈区80字节数据缓冲器用

工作单元

30H

2FH

位地址:

16字节

00H~7FH128可位寻址位

20H

1FH3区

2区

1区32字节4组R0~R7工作寄存器

0区

00H

图2内部数据存储器

二、殊功能寄存器SFR

寻址空间离散分配在:

80H~FFH,

注意PC不在此范围内。

地址末尾为0或8的SFR具有位寻址功能

1、CPU是运算器加控制器

2、算术运算寄存器

(1)累加器A(E0H)

(2)B寄存器:

乘、除法运算用

(3)程序状态字PSW寄存器:

包含程序运行状态信息。

PSWCYACFORS1RS0OV—P

CY(PSW.7)——进位/借位标志;位累加器。

AC(PSW.6)——辅助进/借位标志;用于十进制调整。

F0(PSW.5)——用户定义标志位;软件置位/清零。

OV(PSW.2)——溢出标志;硬件置位/清零。

P(PSW.0)——奇偶标志;A中1的个数为奇数P=1;否则P=0。

RS1、RS0——寄存器区选择控制位。

00:

0区R0~R7

01:

1区R0~R7

10:

2区R0~R7

11:

3区R0~R7

2、指针寄存器

(1)程序计数器PC

PC的内容是指明即将执行的下一条指令的地址,16位,寻址64KB范围,

复位时PC=0000H具有自动加1功能不可寻址即不能通过指令访问。

(2)堆栈指针SP

指明栈顶元素的地址,8位,可软件设置初值,复位时SP=07H

(3)数据指针DPTR

@R0、@R1、@DPTR;指明访问的数据存储器的单元地址,16位,寻址范围64KB。

DPTR=DPH+DPL,也可单独使用。

没有自动加1功能通过软件INCDPTR内容加1

时序

单片机内的各种操作都是在一系列脉冲控制下进行的,而各脉冲在时间上是有 先后顺序的,这种顺序就称为时序。

执令周期:

即从取指到执行完,所需时间。

不同机器指令周期不一样;即使相同机器,不同的指令其指令周期也不一样。

机器周期:

机器的基本操作周期。

一个指令周期含若干机器周期(单、双、四周期)

状态周期:

一个机器周期分6个状态周期Si

每个状态周期含两个振荡周期,即相位P1、P2。

振荡周期:

由振荡时钟产生。

振荡周期Tosc=1/fosc

一个机器周期=12个振荡周期=12×1/fosc。

例如,若fosc=12MHz,则一个机器周期=1μs。

时钟的产生:

通过XTAL1(19)、XTAL(18)。

这两个管脚外部加石英晶体和电容组成振荡器

系统复位

通过给RST管脚加高电平理论上大于两个机器周期,实际大于10ms,系统复后

除了SP=07H,P0、P1、P2、P3为FFH外,所有的寄存器均为00H,PC=0000H,PSW=00H工作寄存器组R0~R7工作在0组。

并行I/O端口

并行I/O端口

四个8位I/O口P0、P1、P2、P3

作为通用I/O使用,是一个准双向口:

“读管脚在输入数据时应先把口置1,使两个FET都截止,引脚处于悬浮状态,可作高阻抗输入”MOVP1.#0FFH

MOVA,P1

读端口数据方式是一种对端口锁存器中数据进行读入的操作方式,CPU读入的这个数据并非端口引脚的数据。

(对端口进行读-修改-写类指令列如CPLP1.0是读端口锁存器而不是管脚)

一、P0口地址80H系统复位后P0=FFH

(1)P0口可作通用I/O口使用,又可作地址/数据总线口;

(2)P0既可按字节寻址,又可按位寻址;

(3)P0作为输入口使用时:

是准双向口;

(4)作通用I/O口输出时:

是开漏输出;(外部管脚必须接上拉电阻)

(5)作地址/数据总线口时,P0是一真正双向口,分时使用,提供地址线A0~A7由ALE控制信号锁存,数据线D0~D7

二、P1口地址90H地址90H系统复位后P1=FFH

2、特点

(1)无地址/数据口功能

(2)可按字节寻址,也可按位寻址

(3)作I/O输入口时:

是一准双向口,不是开漏输出(无需外接上拉电阻)。

三、P2口地址A0H系统复位后P2=FFH

2、特点

(1)当P2口作为通用I/O时,是一准双向口。

(2)从P2口输入数据时,先向锁存器写“1”。

(3)可位寻址,也可按字节寻址

(4)可输出地址高8位A8~A15。

四、P3口地址B0H系统复位后P3=FFH

2、特点

(1)作通用I/O时,是一准双向口,不是开漏输出(无需外接上拉电阻)。

(2)P3口具有第二功能

1、P0口:

地址低8位与数据线分时使用端口,

2、P1口:

按位可编址的输入输出端口,

3、P2口:

地址高8位输出口

4、P3口:

双功能口。

若不用第二功能,也可作通用I/O口。

5、按三总线划分:

地址线:

P0低八位地址,P2高八地址;

数据线:

P0输入输出8位数据;

控制线:

P3口的8位(RXD、TXD、INT0、INT1、T0、T1、WR*、RD*加上PSEN*、ALE、EA组成制总线。

)

中断系统

五个中断源,两个优先级

一、中断请求源(“五源中断”)

五个中断源:

入口地址

外部中断0(/INT0)0003H

T0溢出中断000BH

外部中断1(/INT1)0013H

T1溢出中断001BH

串口中断0023H

有了中断请求,如何通知CPU?

通过中断请求标志位来通知CPU。

外部中断源、定时/计数器的中断请求标志位分布在TCON中;

串口中断标志位分布在SCON中。

TCONTF1TR1TF0TR0IE1IT1IE0IT0

SCONTIRI

中断请求标志位

IE0(INT0)IE1(INT1)TF0(T0)TF1(T1)TI/RI(串口)

TF1——T1的溢出中断标志。

硬件置1,硬件清0(也可软件清0)。

TF0——T0的溢出中断标志。

(同TF1,只是针对T0的)

IE1——外部中断1(/INT1)请求标志。

外部有中断请求时,硬件使IE1置1,硬件清0。

IE0——外部中断0(/INT0)请求标志。

IT1——外部中断1(/INT1)触发类型控制位。

IT1=0,低电平触发。

IT1=1,下降沿触发。

IT0——外中断0(/INT0)触发类型控制位,用法同IT1。

外部中断INT0、INT1触发方式有电平触发和跳变触发

TI——串口发送中断标志位。

发送完数据,硬件使TI置1,软件清0(CLRTI)

RI——串行口接收中断标志位。

硬件置1,软件清0。

二、中断控制(两级管理)

1、中断屏蔽

在中断源与CPU之间有一级控制,类似开关,其中第一级为一个总开关,

第二级为五个分开关,由IE控制。

IEEAESET

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- MCS 51 单片机 复习 要点

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

心电图的基本知识.ppt

心电图的基本知识.ppt