单片机的结构及原理.docx

单片机的结构及原理.docx

- 文档编号:11776236

- 上传时间:2023-04-01

- 格式:DOCX

- 页数:28

- 大小:202.28KB

单片机的结构及原理.docx

《单片机的结构及原理.docx》由会员分享,可在线阅读,更多相关《单片机的结构及原理.docx(28页珍藏版)》请在冰豆网上搜索。

单片机的结构及原理

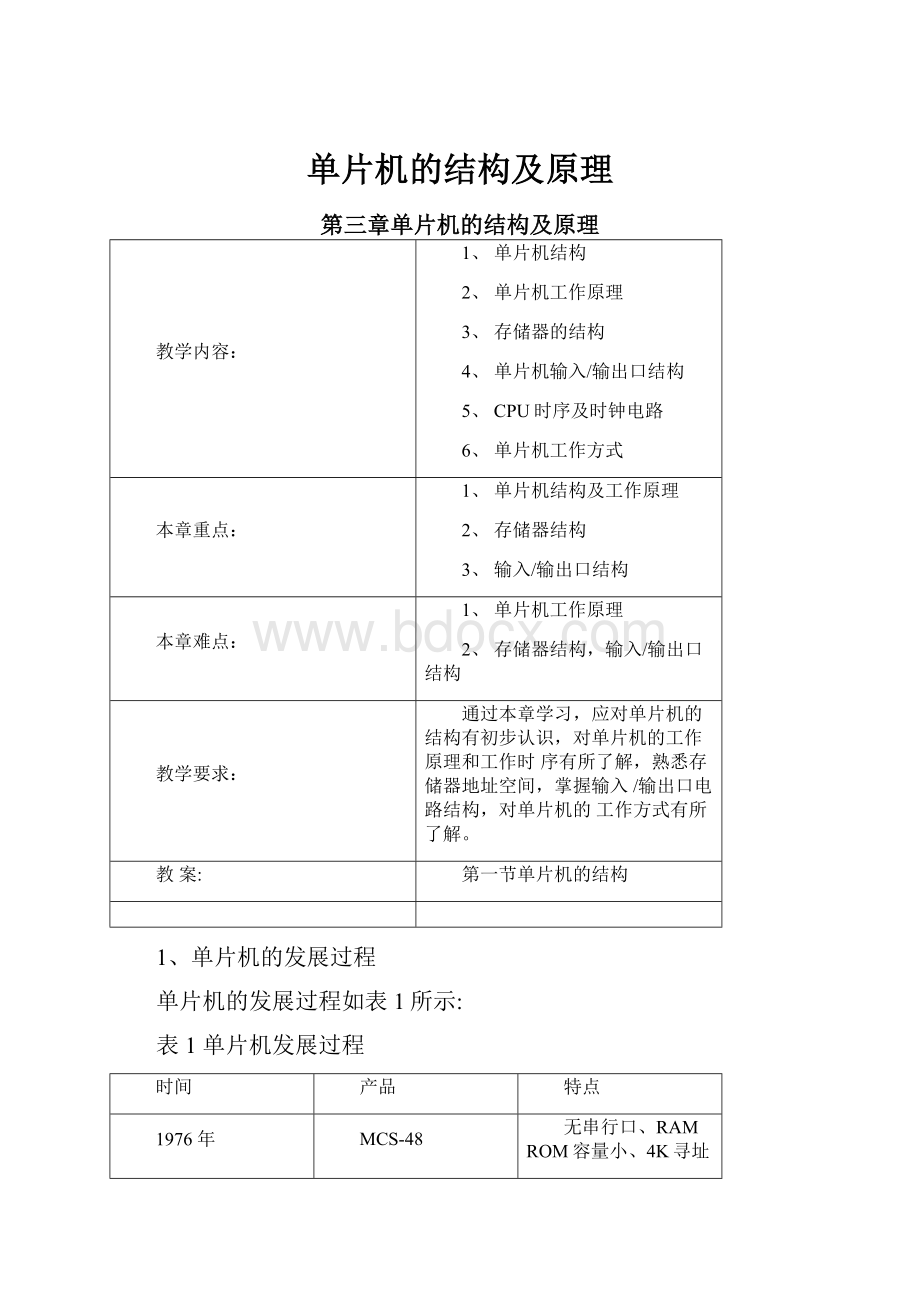

第三章单片机的结构及原理

教学内容:

1、单片机结构

2、单片机工作原理

3、存储器的结构

4、单片机输入/输出口结构

5、CPU时序及时钟电路

6、单片机工作方式

本章重点:

1、单片机结构及工作原理

2、存储器结构

3、输入/输出口结构

本章难点:

1、单片机工作原理

2、存储器结构,输入/输出口结构

教学要求:

通过本章学习,应对单片机的结构有初步认识,对单片机的工作原理和工作时序有所了解,熟悉存储器地址空间,掌握输入/输出口电路结构,对单片机的工作方式有所了解。

教案:

第一节单片机的结构

1、单片机的发展过程

单片机的发展过程如表1所示:

表1单片机发展过程

时间

产品

特点

1976年

MCS-48

无串行口、RAMROM容量小、4K寻址

1980年

MCS-51

8位,集成度咼、

1983年

MCS-96

集成度高、32位、有A/D转换、速度快

1990年

全面发展

高速、大容量、外围集成到内部、性能强

2、单片机生产厂及产品简介

单片机生产厂主要有:

Intel、Motorola、Zilog公司。

从型号来看:

MCS系列、68XXX系列、Z8系列。

从位数来看:

4、&16、32位,

51单片机有80C31(无ROM、80C51(4KROM87C51(4KEPRQM前些年国内教材

和产品开发,基本上以8051系列为使用对象,近年国际上广泛使用80C51单片机,80C51单片机是目前8位机中的佼佼者。

现以80C51为例来介绍单片机的结构。

3、单片机结构

1)、80C51单片机的功能结构

如下图所示,单片机是属于三总线结构,80C51单片机功能方框图如图1所示:

外部中断

■/\

-1

pcPIP^F3

地址/数据

〜

内部中断

控制信号

定时器匚

定时器寸

64K逋线

扩展控制

I/O端口

可编程全双工串行口

振荡器

图1单片机内部结构框图

2)、单片机内容结构

单片机的内部结构如图2所示。

从图中看出,它具有以下特征;适于控制应用的8位CPU

56字节片内数据存储器,分高低两个128字节

4K字节片内程序存储器

64KB程序存储器空间

64KB数据存储器空间

4个8位共32根双向并可按位寻址的I/O口线

两个16位定时/计数器;

一个全双工的串行I/O接口

有5个中断源

片内时钟振荡器

具有布尔处理(位处理)能力

□地址寄存器

V卩」

1FR*R

〒口锁存器-p二口锁存器

RQM/EP^[J1

程序地址-

寄存器

A

n

1T

XT^LL

XI^Ll

][

寄存;

□-

T-'DI.

ICON

THC

TL3

th:

1L1

罪.F(TX

f(RX

JE

F

中断、串行、通道和定时器模块

□sr

0

□驱动器

Il4

J.

■q

J

11

1\■

V1

*

口驱动器

图2单片机内部结构

4、单片机的封装形式、引脚定义及功能

1)、80C51封装

80C51系列单片机具有双列直插式和方形两种封装。

2)、80C51系列单片机引脚功能

1、引脚分布:

如图3所示为双列直插式引脚分布图

2

、引脚功能

VCC----工作电源+5V

GND——电源地

ALE/PROG-----访冋外部存储器时作为低8位地址锁存控制信号;在对EPRO编程时作为编程脉冲输入;在不访问外部存储器和非EPROMg程状态下,该脚输出频率为1/6

单片机晶振频率的方波信号,该信号,可作为时钟脉冲,但在访问数据存储器时会丢失

一个脉冲;

PSEN――外部程序存储器读选通信号.

EA/VPP――访问程序存储器控制信号。

当EA为低电平时,只读外部存储器,当EA为高电平时则先读内部程序存储器,再读外部程序存储器;这个引脚在编程时接编程电压VPP.

RST――复位信号,对系统复位信号要求>2T时频。

XTAL1――片内振荡电路输入端。

XTAL2――片内振荡电路输出端。

P0-P3输入输出端口。

■1-

<1«L-

.=_|•直-.■;■■■-iLn-iL-iL-HiB-aiL

39

IS

強

80C51

图3单片机引脚分布

第二节单片机的工作原理

1、指令与程序

1)、指令

规定计算机执行特定操作的命令,分成操作码和操作数,以二进制编码形式出现,具有固定的格式。

例如:

2000H:

MOVA,#34H

2000H——是标号,即程序地址。

该指令的机械码:

7434H

其中:

74操作码,表示执行何种操作;

34----操作数,表示操作的数据;

2)、程序

程序就是跟据要求编制的指令集合;

例如,将外部数据存储器5000H单元内容送累加器A的程序;

MOVDPTR,#5000H

MOVA,@DPTR

2、CPU的工作原理

CPU是微机的核心部件,由控制器和运算器两部分组成如图4所示。

1)、控制器

控制器由指令部件、时序部件、控制部件三部分组成。

1、指令部件:

由程序计数器、指令寄存器和指令操作码译码器构成。

程序计数器一一用来存放指令的地址的部件。

指令寄存器一一用来暂时存放指令的部件。

指令操作码译码器一一对指令操作码进行分析、解释并在输出端产生各种电平。

2、时序部件:

由时钟系统和节拍发生器构成。

时钟系统一一它产生具有一定频率和宽度的脉冲信号。

节拍发生器一一节拍发生器产生节拍电位和节拍脉冲。

3、微操作控制部件:

对节拍信号和指令操作码信号进行加工处理,产生各种信号

外部总线

图4CPU内部结构

2)、运算器

运算器是数据进行算术运算和逻辑运算的执行部件,单片机不仅有很强的算术运算能力,而且有非常强的位处理能力,因此,特别适合用在实时控制场合。

3)、单片机执行程序的过程

系统复位,程序计数器PC的值为0000H

在控制信号的作用下,根据PC值从内存单元中取出相应的指令。

将取出的指令送指令寄存器,经指令译码器分析,译码信号与时序信号合成,形成所需的各种微操作信号。

循环往复执行,直到结束。

第三节存储器结构

1、单片机存储器空间分布

如图5所示,80C51单片机存储器在物理结构上分片内程序存储器、片外程序存储器、片内数据存储器、片外数据存储器四个空间;在逻辑结构上(使用上)分成片内外统一编址的64KB程序存储器、256B的片内数据存储器以及64KB片外数据存储器。

在访问不同的存储器空间时,使用的指令不同。

片内存储器

FTFFH

Lj

■=、11

M1

片外ROM

rFfFH

"1丨

片外RAM

(I/O)

E-二

vwwwn

C:

H

片外扩展存储器

图5单片机存储器结构

2、程序存储器

1)、程序存储器的作用

用来存放操作程序。

2)、程序存储器的空间分布

分片内和片外,共64KB空间,EA=1,先访问片内程序存储器再访问片外存储器,其地址是连续的;当EA=O时,只访问片程序存储器。

复位时PC=OOOOH,值得注意的是,程序存储器从OOO3H〜OO3OH共4O个单元作为中断处理用,如表2所示:

表2中断入口地址

地址空间

字节数

说明

OOO3H~OOOAH

8

外部中断O入口

OOOBH~OO12H

8

定时器O溢出中断入口

OO13H~OO1AH

8

外部中断1入口

OO1BH~OO22H

8

定时器1溢出中断入口

OO23H~OO3OH

8

串行口中断入口

3、数据存储器

1)、数据存储器的作用

数据存储器用于存放中间运算结果、数据暂存和缓冲、标志位等。

2)、数据存储器空间分布

数据存储器由片内256字节(含低128单元和高128单元)和片外64KB两个存储空

间组成,结构如图6所示:

F面分别说明:

(1)、片内数据存储器

片内256B的数据存储器分高128B和低128B两部分

1、低128字节

工作寄存器区:

地址从OOH—1FH,共32个字节,每8个字节构成一个区,记作R0-R7。

寄存器区的选择由程序状态字PSW中的RSO位和RS1位的值定:

系统复位时,系统自动指向工作寄存器0区。

工作寄存器一般用作数据缓冲寄存器,如果

不用作工作寄存器,这个区域中的32个字节

也可以作数据寄存器使用,直接按字节寻址。

位寻址区:

该区域地址从20H到2FH共16个字节,128位,使用指令可以寻址到位,位地址OOH—7FH

注意:

这个区域也可按字节寻址。

数据区:

地址从3OH—7FH,共8O个字节。

可作为用户数据存储器,按字节访问,

用户堆栈通常在该区域开辟。

2、高128B(特殊功能寄存器区SFR

8OC51把CPU中的专用寄存器、并行端口锁存器、串行口、定时器/计数器内的控制寄存器等集中安排在一个区域(共21个专用寄存器),离散地分布在地址从8OH到FFH范围内,这个区域称为特殊功能寄存器区。

它共有128个字节,在物理上与片内RA腕别

占有高128字节地址和低128字节地址。

构成了连续的256个字节空间,在性质上都属于数据存储器。

下面介绍常用的SFR对在本节尚未介绍的其它SFR在后面介绍。

累加器Acc:

Acc是一个具有特殊用途的8位寄存器,主要用存放操作数和运算结果。

例如:

ADDA,#55H表示累加器A的内容与55H相加,结果放到累加器中并暂存起来。

程序状态字PSWPSV是一个可编程的8位寄存器,如图7所示,用来存放当前指令执行结果的有关状态。

单片机有许多指令的执行会影响PSW勺位状态。

PSW勺位状态可通

过指令设置,它是一个可以位寻址的特殊寄存器

高地址

低地址

高地址

低地址

图7状态寄存器

例如:

单片机在运算,Y=84+105时,会发生溢出错误,因为运算结果189,已经超出-128--+127的范围。

寄存器B:

寄存器B是一个8位寄存器,主要用于乘除法。

乘法运算时,B是乘数,乘法操作后,积的高8位存于B中;除法运算时,B是除数,除法操作后,余数存于B中。

此外,B寄存器也可作为一般数据寄存器使用。

堆栈指钍:

堆栈指钍(SP):

是专门用来指示椎栈的起始位置的8位寄存器,地址在81H,复位

时堆栈指钍初始

化地址为07H,用户开辟堆栈时必须指明SP的初始值(栈底)和长度,如图8所示。

注意:

堆栈的存贮区域在RAM勺30H-7FH之间。

进栈用PUSH出栈用POP

堆栈---堆栈是在RAM中由用户开辟的一个区域。

在这个区域中数据的存取是按“先进后出的原则”进行。

在这个区域的数据是不能按字节访问的,它是专用来为程序中断、子程序调用等临时保护现场的一个存储空间。

数据指钍DPTR数据指钍是一个16位地址寄存器,由高位字节DPH和低位字节DPL组成,这两个字节也可单独作为8位寄存器使用。

使用DPTF可以访问64K字节外部数据存储器的任一单元。

例如:

MOVDPTR#dataMOVXA@DPTR

这两条指令的意思是:

把常数data传送到DPTR再把DPTR^指向的外部RAM单元的数据送入累加器中。

(2)、外部数据存储器

64KB的外部数据存储器是通过扩展而形成的,外部数据存储器地址从OOOOH-FFFFH

夕卜部存储器的访问只能间接寻址。

第四节单片机输入/输出口结构

1、P0端口(如图9所示)

1)、作为通用I/O口使用

内部控制信号为0电平,此时,与门将封锁上拉场效应管,MU)接通锁存器的反向输出端。

由于T1处于断路状态,因此在输出端要接上拉电阻(5-10KQ),P0口的工作过程如下:

1、数据输出:

内部的写脉冲加在D触发器的CL端,数据从总线写入D,并向端口引脚输出。

2、数据输入(分读引脚和读端口两种情况):

读引脚:

读引脚信号打开三态缓冲器,信号通过三态门传送到内部总线•

读端口:

读端口则是通过读锁存器实现的。

注意:

数据输入,口线必须先置1,否则读数有可能出错;P0口作通用I/O口使用时,无论输入还是输出,必须接上拉电阻;

2)、作地址/数据总线使用

P0口作为总线使用时,内部发出控制信号,打开上面的与门,MU)接通地址/数据线,地址和数据分时工作。

读锁存器

内部总线

写锁存器

读引脚

图9P0口结构

2、P1端口(如图10所示)

1)、数据输出:

系统发出写锁存器命令,内部总线的数据通过D锁存器FET从引脚输出。

2)、数据输入:

先向锁存器写入1封锁FET,引脚信号在读引脚控制信号下由引脚通

过三态门传入内部总线(注意在编程时要先将该位先置1再输入数据)。

读锁存器.一JL

I

内部总线J

h

lil-x」

PET

写锁存器

锁存器一

C

1

读引脚

3、P2端口(如图11所示)

P2口可作为通用I/O口和高位地址线使用。

作通用I/O口时控制信号使MUXS锁存器,内部上拉电阻被截断,作地址线时MUX与地址线相联。

1)、P2口作通用I/O口使用

输出:

在写锁存器控制下,内部总线的数据通过D输出到引脚。

输入:

在读引脚控制下,数据从三态门输入到内部总线(同样要接上拉电阻,要置1

指令)。

读引脚

读锁存器

内部总线

写锁存器

图11P2口结构

2)、作总线使用

控制信号使地址与输出相联,与门接通,内部上拉电阻有效。

P2与P0配合作地址线的高8位。

此时就不能作通用的I/O口使用了

3)注意事项

1、单片机外部不接程序存储器时,如果外部数据存储器只有256B,则可使用MOVXA,@Ri指令访问。

在这个过程中,地址由P0口输出,P2口不变。

2、如果外部存储容量较大(或外部接程序存储器),需用MOVXA,@DTPR指令访问。

此时,P0,P2将分别输出高低地址。

值得注意的是在输出地址的过程中,P2口的锁存器内容始终保持不变,因此在输出地址后,P2口可作通用的I/O口使用。

3、如果单片机外部接有程序存储器,由于程序是在不断进行,因此P2口,在这种

状态下是不能再你通用I/O口使用

4、P3端口(如图12所示)

1)、第一功能使用

输出:

此时,“第二输出功能”为高电平,与非门打开,内部数据通过锁存器的Q经过与非门到T;

输入:

从引脚在读引脚控制信号控制下,通过三态门进入(同样要置1)。

2)、第二功能使用

P3口的第二功能;

读锁存器

内部总线

写锁存器

读引脚

I

第二功能输入

图12P3口结构

P3.0

RXD

(串行数据输入口)

P3.1

TXD

(串行数据输出口)

P3.2

INT

0(外部中断0)

P3.3

INT

1(外部中断1)

P3.4

To

(定时器/计数器0外部输入)

P3.5

T1

(定时器/计数器1外部输入)

P3.6

WR

(外部数据存储器写脉冲)

P3.7

RD

(外部数据存储器读脉冲)

当P3口作为第二功能使用时,此时Q为高电平,与非门打开,数据从“第二输出功能”端输出;输入时,端口引脚的“第二功能信号”通过缓冲器送到第二输入功能端。

5、端口负载能力和接口要求

1)、P0口可带动8个LSTTL(在TTL电路基础上研制的一种低功耗电路)。

既可作通用I/O口使用,也可作地址/数据线使用,作I/O口使用时,要接上拉电阻,作地址/数据使用时,不须接上拉电阻,此时,不能再作I/O口使用。

2)、P1—P3口输出可带动4个LSTTL电路和MOSfe路。

3)、P0-P3均为双向I/O口,作输入时,必须先在端口锁存器上写“1”。

第五节CPU寸序及时钟电路

CPU从取指令、分析指令到执行指令的全过程中,都是在时序控制下一拍一拍地进行的。

下面介绍时序的几个概念:

时钟周期

时钟周期又叫节拍,定义为时钟脉冲频率的的倒数,如f=12MHZ,则T=1/12,

在单片机中,节拍用P表示,二个节拍定义为一个状态,状态用S表示,

机器周期

CPU完成一种基本操作所需的时间称机器周期。

如CPU取指令、分析指令、执行指令等。

一个机器周期分6个状态,记为S1—S6,因此,一个周期由12个节拍组成,分别记为S1P1、S1P2、,,S6P1、S6P2。

指令周期

CPU执行一条指令所需要的时间称之为指令周期,如图13所示。

图13单片机指令周期

1、指令时序

1)、取指令和执行指令:

取指令:

CPU在每出现一次ALE取一次指令,一个周期出现二次ALE第一次出现在S1P2第二次出现在S4P2宽度为一个状态。

执行指令:

80C51共有111条指令,指令时序分成单字节、单周期指令时序;双字节单周期指令时序;单字节双周期指令时序;二字节二周期指令时序;一字节四周期指令时序。

2)、指令执行过程

如图14是单片机指令执行过程:

机器周期

机器周期

S6

M3

S3

ALE

读下一个操作码(丢失)

渎操作码

女如:

INCA

|S

驚1.

"I

■XJ-

字节,1周期指令,如:

ADD

A#data

厂读操作码「一读第二字节I

S2|S3戊刃|S^|SG!

字节,2周期指令,如:

INCDPTR

厂读操作码「下一个操作码丫

字节指令字节周期,

PIs?

T~-

IS4

|S1[.

读下一个操作码

1

1

1

读下一个操作码

-读操作码

I

J

Ci

■-J

3

[j■:

Isr[.

失)

图14单片机指令执行过程

现说明如下:

1、单字节、单周期指令时序:

在S1期间读入操作码,并把它送入指令寄存器,接着开始执行,并在本周期的S2P2执行完毕。

如:

INCA;

2、双字节单周期指令时序:

在S1期间读入指令操作码并锁存,在S4期间读入指令第二字节,指令在相周期的

S6P2期间执行完毕。

如:

ADDA,#data

3、单字节双周期指令时序:

在S1期间读入操作码并锁存,然后开始执行,在第二周期的最后一个状态S6P2执

行完毕。

如:

MOVXA@DPTR

2、振荡器和时钟电路

如图15所示,80C51的时钟主生方法分内部时钟方式和

外部时钟方式:

1)、内部时钟电路图15振荡器

此时在芯片XTAL1和XTAL2两端跨接晶体,C取30PF;若跨接陶瓷谐振器,

C取47pF;晶振频率可在1.2~12MHZ之间选择。

2)、外部时钟方式

此方式是利用外部振荡脉冲接

外部时钟输入

8051外时钟源接法

80C51外时钟源接法

图16单片机外接时钟电路

入XTAL1或XTAL2。

HMOS和CHMOS单片机外时钟信

号接入方式不同。

如图16所示:

8051的时钟信号由XTAL2输入,考虑到XTAL2不是TTL电平,因此接有上拉电阻。

80C51的时钟由XTAL1输入。

第六节单片机工作方式

单片机有复位、程序执行、低功耗、编程和校验四种工作方式,下面介绍前三种,

编程和校验工作方式。

1、复位方式

1)复位操作

复位操作是单片机的初始化操作,单片机在进入运行前和在运行过程中程序出错或操作失误使系统不能正常运行时,需要进行复位操作。

复位操作后,程序将从0000H开始

重新执行,复位时特殊功能寄存器的状态如表3所示。

除此之外,复位操作还使单片机的ALE和PSEN引脚信号在复位期间变为无效状态。

表3特殊功能寄存器复位状态表

寄存器名称

复位状态

寄存器名称

复位状态

PC

0000H

TCON

0X000000B

ACC

00H

TL0

00H

B

00H

TH0

00H

PSW

00H

TL1

00H

SP

07H

TH1

00H

TMOD

XX000000B

PCON

0XXX0000B

DPTR

0000H

SBUF

不定

P0-P3

FFH

SCON

00H

2)复位工作方式

(1)复位信号

单片机对复位信号的要求:

一是复位信号为高电平,二是复位信号有效持续时间不少于24个振荡脉冲(两个机器周期)以上。

在这里特别要提醒的是,在一个应用系统中,如果有几片单片机同时工作,在程序上有连接关系,系统复位时,应确保每一片单片机同时复位。

(2)复位工作方式

复位信号由单片机的RST引脚输入,复位操作有上电自动复位、按键复位和外部脉冲复位三种方式,见图2.5所示。

随着单片机技术的发展,目前有些单片机内部带有看门狗电路,当程序进行出错或进入了无休止循环时,看门狗电路将利用软件强行使系统复

位。

2、程序执行方式

程序执行方式是单片机的基本工作方式。

系统复位PC=OOOOH,程序从0000H开始执

行,考虑到单片机存储器结构的特殊性(0003H-0002BH共四十个单元,预留用于中断程序),在0000H-0002H中放一条无条件转移指令,程序从指定的地址开始执行。

配合程序调试,程序又可运行在单步、跟踪、全速运行三种执行方式。

目前一般仿真器都提供了这三种程序执行方式。

随着科学技术的发展,在线可编程(ISP)单片机已经走向应用,如STT89C58、AT89S51、AT89S52芯片,都具有在线可编程功能。

3、低功耗工作方式

MCS-51单片机有待机和掉电保护两种低功耗工作方式,单片机低功耗方式的设置是通过电源控制寄存器(PCON的相关位来实现的。

电源控制寄存器如下:

MSB

LSB

SMOD

-

-

-

GF1

GF0

PD

IDL

SMOD波特率培增位,在串行通信时使用,用来辅助设置通信速度

GF1通用标志位1。

GF0通用标志位0。

PD掉电方式设置位,PD=1进入掉电工作方式。

PCON是一个8位的寄存器,不具备位寻址功能,设置任意一位都要通过字节寻址命令。

如:

进入掉电工作方式:

MOVPCO,N#02H进入待机工作方式:

MOVPCO,N#01H

1)、待机工作方式

(1)待机工作方式特征

系统进入待机工作方式,CPU亭止工作,与cpu相关的特殊功能寄存器和全部通用寄存器被“冻结”在原状态,此时振荡器仍在工作,中断功能继续存在。

(2)进入待机工作方式设置

要使系统进入待机工作方式,只要寄存器PCON中的IDL=1即可。

指令MOVPCON#01H实现待机工作方式设置。

(3)退出待机工作方式在待机工作方式下,通过引入外中断信号的方法,使待

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 单片机 结构 原理

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx