EDA的一些程序代码.docx

EDA的一些程序代码.docx

- 文档编号:11725798

- 上传时间:2023-03-31

- 格式:DOCX

- 页数:32

- 大小:735.94KB

EDA的一些程序代码.docx

《EDA的一些程序代码.docx》由会员分享,可在线阅读,更多相关《EDA的一些程序代码.docx(32页珍藏版)》请在冰豆网上搜索。

EDA的一些程序代码

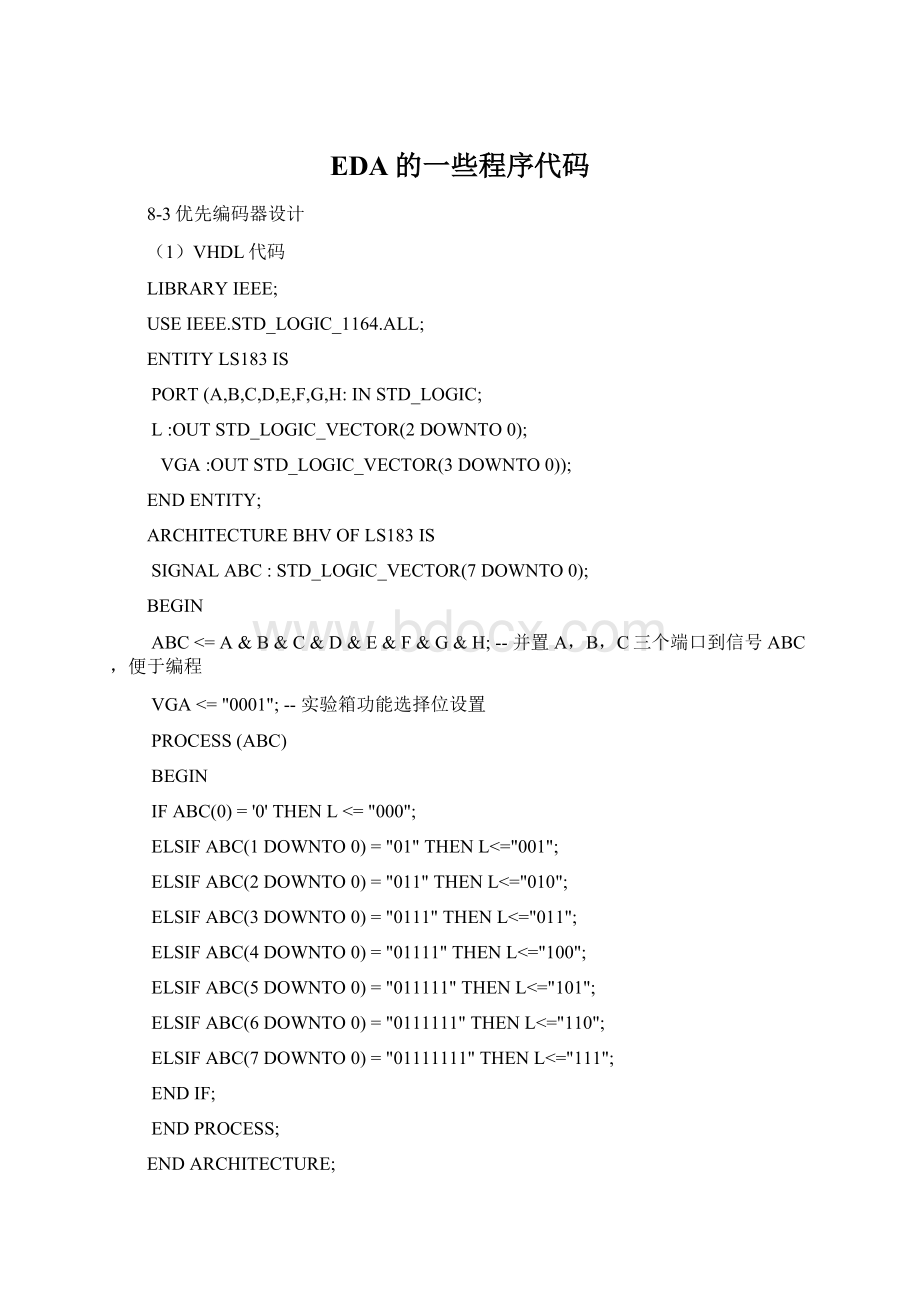

8-3优先编码器设计

(1)VHDL代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLS183IS

PORT(A,B,C,D,E,F,G,H:

INSTD_LOGIC;

L:

OUTSTD_LOGIC_VECTOR(2DOWNTO0);

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDENTITY;

ARCHITECTUREBHVOFLS183IS

SIGNALABC:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

ABC<=A&B&C&D&E&F&G&H;--并置A,B,C三个端口到信号ABC,便于编程

VGA<="0001";--实验箱功能选择位设置

PROCESS(ABC)

BEGIN

IFABC(0)='0'THENL<="000";

ELSIFABC(1DOWNTO0)="01"THENL<="001";

ELSIFABC(2DOWNTO0)="011"THENL<="010";

ELSIFABC(3DOWNTO0)="0111"THENL<="011";

ELSIFABC(4DOWNTO0)="01111"THENL<="100";

ELSIFABC(5DOWNTO0)="011111"THENL<="101";

ELSIFABC(6DOWNTO0)="0111111"THENL<="110";

ELSIFABC(7DOWNTO0)="01111111"THENL<="111";

ENDIF;

ENDPROCESS;

ENDARCHITECTURE;

时序仿真TestBench文件内容(不含注释)及仿真波形图

仿真时制作的TestBench文件添加:

WAITFOR200ns;A<='0';B<='1';C<='1';D<='1';E<='1';F<='1';G<='1';H<='0';

WAITFOR200ns;A<='1';B<='0';C<='1';D<='1';E<='1';F<='1';G<='0';H<='1';

WAITFOR200ns;A<='1';B<='1';C<='0';D<='0';E<='0';F<='0';G<='1';H<='1';

WAITFOR200ns;A<='1';B<='1';C<='1';D<='0';E<='0';F<='1';G<='1';H<='1';

WAITFOR200ns;A<='1';B<='1';C<='1';D<='0';E<='1';F<='1';G<='1';H<='1';

WAITFOR200ns;A<='1';B<='1';C<='0';D<='1';E<='1';F<='1';G<='1';H<='1';

WAITFOR200ns;A<='1';B<='0';C<='1';D<='1';E<='1';F<='1';G<='1';H<='1';

WAITFOR200ns;A<='0';B<='1';C<='1';D<='1';E<='1';F<='1';G<='1';H<='1';

8421码奇偶校验位发生器设计

(1)VHDL代码

LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;

ENTITYxor42IS

PORT(B8,B4,B2,B1:

INSTD_LOGIC;

P,NP:

OUTSTD_LOGIC;

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDENTITY;

ARCHITECTUREBHVOFXOR42IS

SIGNALe,f,g:

STD_LOGIC;

BEGIN

VGA<="0001";

e<=B8XORB4;

f<=B2XORB1;

g<=eXORf;

p<=g;

NP<=gXOR'1';

ENDARCHITECTURE;

注意:

在Entity中务必添加VGA功能选择端口:

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

在Architecture中务必添加功能选择设置:

VGA<="0001";

(2)时序仿真TestBench文件内容(不含注释)及仿真波形图

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYxor42_vhd_tstIS

ENDxor42_vhd_tst;

ARCHITECTURExor42_archOFxor42_vhd_tstIS

--constants

--signals

SIGNALB1:

STD_LOGIC;

SIGNALB2:

STD_LOGIC;

SIGNALB4:

STD_LOGIC;

SIGNALB8:

STD_LOGIC;

SIGNALNP:

STD_LOGIC;

SIGNALP:

STD_LOGIC;

SIGNALVGA:

STD_LOGIC_VECTOR(3DOWNTO0);

COMPONENTxor42

PORT(

B1:

INSTD_LOGIC;

B2:

INSTD_LOGIC;

B4:

INSTD_LOGIC;

B8:

INSTD_LOGIC;

NP:

OUTSTD_LOGIC;

P:

OUTSTD_LOGIC;

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

);

ENDCOMPONENT;

BEGIN

i1:

xor42

PORTMAP(

--listconnectionsbetweenmasterportsandsignals

B1=>B1,

B2=>B2,

B4=>B4,

B8=>B8,

NP=>NP,

P=>P,

VGA=>VGA

);

init:

PROCESS

--variabledeclarations

BEGIN

--codethatexecutesonlyonce

WAITFOR100ns;B8<='0';B4<='0';B2<='0';B1<='0';

WAITFOR100ns;B8<='0';B4<='0';B2<='0';B1<='1';

WAITFOR100ns;B8<='0';B4<='0';B2<='1';B1<='0';

WAITFOR100ns;B8<='0';B4<='0';B2<='1';B1<='1';

WAITFOR100ns;B8<='0';B4<='1';B2<='0';B1<='0';

WAITFOR100ns;B8<='0';B4<='1';B2<='0';B1<='1';

WAITFOR100ns;B8<='0';B4<='1';B2<='1';B1<='0';

WAITFOR100ns;B8<='0';B4<='1';B2<='1';B1<='1';

WAITFOR100ns;B8<='1';B4<='0';B2<='0';B1<='0';

WAITFOR100ns;B8<='1';B4<='0';B2<='0';B1<='1';

WAITFOR100ns;B8<='1';B4<='0';B2<='1';B1<='0';

WAITFOR100ns;B8<='1';B4<='0';B2<='1';B1<='1';

WAITFOR100ns;B8<='1';B4<='1';B2<='0';B1<='0';

WAITFOR100ns;B8<='1';B4<='1';B2<='0';B1<='1';

WAITFOR100ns;B8<='1';B4<='1';B2<='1';B1<='0';

WAITFOR100ns;B8<='1';B4<='1';B2<='1';B1<='1';

WAIT;

ENDPROCESSinit;

always:

PROCESS

--optionalsensitivitylist

--()

--variabledeclarations

BEGIN

--codeexecutesforeveryeventonsensitivitylist

WAIT;

ENDPROCESSalways;

ENDxor42_arch;\

半加器设计

(1)VHDL代码

LIBRARYIEEE;--半加器

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYh_adderIS

PORT(a,b:

INSTD_LOGIC;

co,so:

OUTSTD_LOGIC);

ENDENTITY;

ARCHITECTUREfh1OFh_adderIS

SIGNALabc:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

abc<=a&b;

PROCESS(abc)

BEGIN

CASEabcIS

WHEN"00"=>so<='0';co<='0';

WHEN"01"=>so<='1';co<='0';

WHEN"10"=>so<='1';co<='0';

WHEN"11"=>so<='0';co<='1';

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

ENDARCHITECTUREfh1;

注意:

在Entity中务必添加VGA功能选择端口:

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

在Architecture中务必添加功能选择设置:

VGA<="0001";

(2)时序仿真TestBench文件内容(不含注释)及仿真波形图

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYf_adder_vhd_tstIS

ENDf_adder_vhd_tst;

ARCHITECTUREf_adder_archOFf_adder_vhd_tstIS

--constants

--signals

SIGNALain:

STD_LOGIC;

SIGNALbin:

STD_LOGIC;

SIGNALcin:

STD_LOGIC;

SIGNALcout:

STD_LOGIC;

SIGNALsum:

STD_LOGIC;

SIGNALVGA:

STD_LOGIC_VECTOR(3DOWNTO0);

COMPONENTf_adder

PORT(

ain:

INSTD_LOGIC;

bin:

INSTD_LOGIC;

cin:

INSTD_LOGIC;

cout:

OUTSTD_LOGIC;

sum:

OUTSTD_LOGIC;

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

);

ENDCOMPONENT;

BEGIN

i1:

f_adder

PORTMAP(

--listconnectionsbetweenmasterportsandsignals

ain=>ain,

bin=>bin,

cin=>cin,

cout=>cout,

sum=>sum,

VGA=>VGA

);

init:

PROCESS

--variabledeclarations

BEGIN

--codethatexecutesonlyonce

WAITFOR100ns;ain<='0';bin<='0';cin<='0';

WAITFOR100ns;ain<='0';bin<='0';cin<='1';

WAITFOR100ns;ain<='0';bin<='1';cin<='0';

WAITFOR100ns;ain<='0';bin<='1';cin<='1';

WAITFOR100ns;ain<='1';bin<='0';cin<='0';

WAITFOR100ns;ain<='1';bin<='0';cin<='1';

WAITFOR100ns;ain<='1';bin<='1';cin<='0';

WAITFOR100ns;ain<='1';bin<='1';cin<='1';

WAIT;

ENDPROCESSinit;

always:

PROCESS

--optionalsensitivitylist

--()

--variabledeclarations

BEGIN

--codeexecutesforeveryeventonsensitivitylist

WAIT;

ENDPROCESSalways;

ENDf_adder_arch;

带使能输入及同步清零的增1计数器

(1)VHDL代码

注意:

在Entity中务必添加VGA功能选择端口:

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

在Architecture中务必添加功能选择设置:

VGA<="0001";

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT16IS

PORT(CLK,CLR,EN:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCNT16;

ARCHITECTUREbehavOFCNT16IS

BEGIN

VGA<="0001";

PROCESS(CLK,CLR,EN)

VARIABLEQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFCLR='1'THENQI:

=(OTHERS=>'0');

ELSIFCLK'EVENTANDCLK='1'THEN

IFEN='1'THENQI:

=QI+1;

ELSEQI:

=(OTHERS=>'0');

ENDIF;

ENDIF;

Q<=QI;

ENDPROCESS;

ENDbehav;

(2)时序仿真TestBench文件内容(不含注释)及仿真波形图

生成TestBench模板文件,做以下修改:

在Architecture的常数声明部分添加

……

--constants

CONSTANTclk_period:

TIME:

=40ns;--该常数用于设置时钟周期,40ns

两个进程修改如下:

init:

PROCESS

--variabledeclarations

BEGIN

--codethatexecutesonlyonce

WAITFOR100ns;en<='1';

WAITFOR1500ns;clr<='1';

WAITFOR200ns;clr<='0';

WAIT;

ENDPROCESSinit;

always:

PROCESS

BEGIN

--codeexecutesforeveryeventonsensitivitylist

clk<='1';WAITFORclk_period/2;--时钟信号的TestBench的一般描述

clk<='0';WAITFORclk_period/2;

ENDPROCESSalways;

……

其中黑体部分,是时钟信号仿真TestBench的描述方式之一。

完成时序仿真,保存波形截图。

带使能输入、进位输出及同步清零的增1十进制计数器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT10IS

PORT(CLK,CLR,EN:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC;

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCNT10;

ARCHITECTUREbehavOFCNT10IS

BEGIN

VGA<="0001";

PROCESS(CLK,CLR,EN)

VARIABLEQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFCLR='1'THENQI:

=(OTHERS=>'0');

ELSIFCLK'EVENTANDCLK='1'THEN

IFEN='1'THENQI:

=QI+1;

ELSEQI:

=(OTHERS=>'0');

ENDIF;

ENDIF;

IFQI=9THENCOUT<='1';

ELSECOUT<='0';

ENDIF;

Q<=QI;

ENDPROCESS;

ENDbehav;

(2)时序仿真TestBench文件内容(不含注释)及仿真波形图

--constants

CONSTANTclk_period:

TIME:

=40ns;

--signals

--variabledeclarations

BEGIN

--codeexecutesforeveryeventonsensitivitylist

clk<='1';WAITFORclk_period/2;

clk<='0';WAITFORclk_period/2;

ENDPROCESSalways;

基本串入/并出移位寄存器

(1)VHDL代码

注意:

在Entity中务必添加VGA功能选择端口:

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

在Architecture中务必添加功能选择设置:

VGA<="0001";

libraryieee;

useieee.std_logic_1164.all;

entitysb8is

port(clk,din:

instd_logic;

dout:

outstd_logic_vector(7downto0);

VGA:

outstd_logic_vector(3downto0));

endentity;

architectureoneofsb8is

begin

VGA<="0001";

process(clk)

variablereg8:

std_logic_vector(7downto0):

="00000000";

begin

ifclk'eventandclk='1'then

reg8(7downto1):

=reg8(6downto0);

reg8(0):

=din;

endif;

dout<=reg8;

endprocess;

endarchitecture;

(2)时序仿真TestBench文件内容(不含注释)及仿真波形图

时序仿真TestBench文件内容:

……

--constants

CONSTANTclk_period:

TIME:

=40ns;

……

init:

PROCESS

--variabledeclarations

BEGIN

--codethatexecutesonlyonce

WAITFOR40ns;din<='1';

WAITFOR40ns;din<='0';

WAITFOR40ns;din<='1';

WAITFOR40ns;din<='0';

WAIT;

ENDPROCESSinit;

always:

PROCESS

BEGIN

--codeexecutesforeveryeventonsensitivitylist

clk<='1';WAITFORclk_period/2;

clk<='0';WAITFORclk_period/2;

ENDPROCESSalways;

……

仿真波形图:

改进的串入/并出移位寄存器

(1)Top-LevelDesignVHDL代码

注意:

在Entity中务必添加VGA模式端口:

VGA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

在Architecture中务必添加模式设定:

VGA<="0001";

libraryieee;

useieee.std_logic_1164.all;

entitysb88is

port(clk,din:

instd_logic;

dout:

outstd_logic_vector(3downto0);

VGA:

outstd_logic_vector(3downto0));

endentity;

architectureoneofsb88is

begin

VGA<="0001";

process(clk)

variablereg8:

std_logic_vector(3downto0);

variablej:

integer:

=1;

begin

ifj>4then

dout<=reg8;

j:

=1;

elsif

clk'eventandclk='1'then

j:

=j+1;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 一些 程序代码

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx

出货单(范本).xls

出货单(范本).xls

多级涡轮密封泄漏的数值模拟.pptx

多级涡轮密封泄漏的数值模拟.pptx