第五章 可编程逻辑 习题答案白中英主编第五版.docx

第五章 可编程逻辑 习题答案白中英主编第五版.docx

- 文档编号:11538521

- 上传时间:2023-03-19

- 格式:DOCX

- 页数:18

- 大小:52.54KB

第五章 可编程逻辑 习题答案白中英主编第五版.docx

《第五章 可编程逻辑 习题答案白中英主编第五版.docx》由会员分享,可在线阅读,更多相关《第五章 可编程逻辑 习题答案白中英主编第五版.docx(18页珍藏版)》请在冰豆网上搜索。

第五章可编程逻辑习题答案白中英主编第五版

第五章可编程逻辑(习题答案)

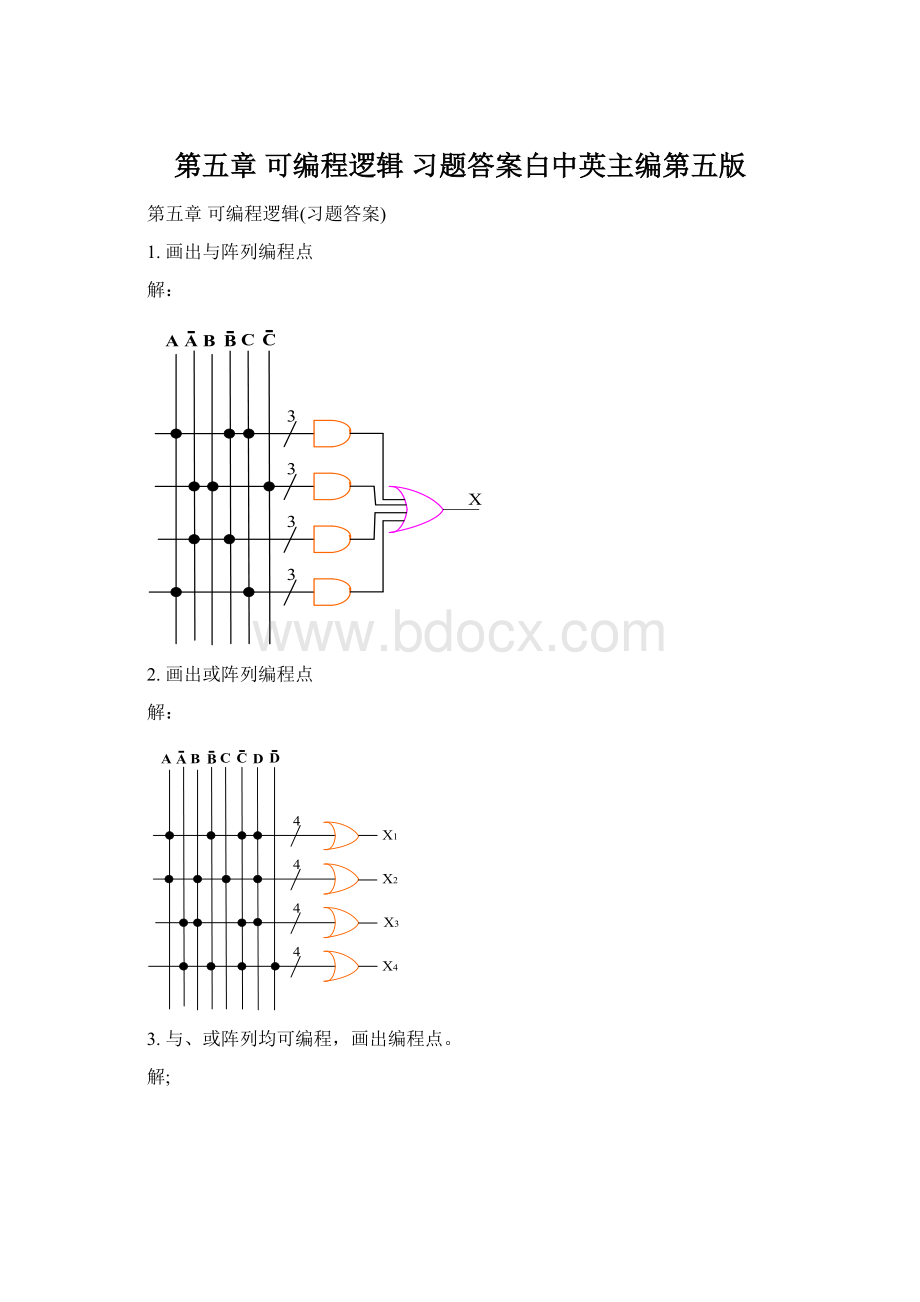

1.画出与阵列编程点

解:

2.画出或阵列编程点

解:

3.与、或阵列均可编程,画出编程点。

解;

4.4变量LUT编程

解:

5.用VHDL写出4输入与门

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYand4IS

PORT(a,b,c,d:

INSTD_LOGIC;

x:

OUTSTD_LOGIC);

ENDand4;

ARCHITECTUREand4_arcOFand4IS

BEGIN

x<=aANDbANDcANDd;

ENDand4_arc;

6.用VHDL写出4输入或门

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYor4IS

PORT(a,b,c,d:

INSTD_LOGIC;

x:

OUTSTD_LOGIC);

ENDor4;

ARCHITECTUREor4_arcOFor4IS

BEGIN

x<=aORbORcORd;

ENDor4_arc;

7.用VHDL写出SOP表达式

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYsopIS

PORT(a,b,c,d,e,f:

INSTD_LOGIC;

x:

OUTSTD_LOGIC);

ENDsop;

ARCHITECTUREsop_arcOFsopIS

BEGIN

x<=(aANDb)OR(cANDd)OR(eANDf);

ENDsop_arc;

8.用VHDL写出布尔表达式

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYbooleanIS

PORT(a,b,c:

INSTD_LOGIC;

f:

OUTSTD_LOGIC);

ENDboolean;

ARCHITECTUREboolean_arcOFbooleanIS

BEGIN

f<=(aOR(NOTb)ORc)AND(aORbOR(NOTc))AND((NOTa)OR(NOTb)OR(NOTc));

ENDboolean_arc;

9.用VHDL结构法写出SOP表达式

解:

源代码:

――三输入与非门的逻辑描述

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYnand3IS

PORT(a,b,c:

INSTD_LOGIC;

x:

OUTSTD_LOGIC);

ENDnand3;

ARCHITECTUREnand3_arcOFnand3IS

BEGIN

x<=NOT(aANDbANDc);

ENDnand3_arc;

――顶层结构描述文件

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYsopIS

PORT(in1,in2,in3,in4,in5,in6,in7,in8,in9:

INSTD_LOGIC;

out4:

OUTSTD_LOGIC);

ENDsop;

ARCHITECTUREsop_arcOFsopIS

COMPONENTnand3

PORT(a,b,c:

INSTD_LOGIC;

x:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALout1,out2,out3:

STD_LOGIC;

BEGIN

u1:

nand3PORTMAP(in1,in2,in3,out1);

u2:

nand3PORTMAP(in4,in5,in6,out2);

u3:

nand3PORTMAP(in7,in8,in9,out3);

u4:

nand3PORTMAP(out1,out2,out3,out4);

ENDsop;

10.用VHDL数据流法写出SOP表达式

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYsopIS

PORT(in1,in2,in3,in4,in5,in6,in7,in8,in9:

INSTD_LOGIC;

out4:

OUTSTD_LOGIC);

ENDsop;

ARCHITECTUREsop_arcOFsopIS

BEGIN

out4<=(in1ANDin2ANDin3)OR(in4ANDin5ANDin6)OR(in7ANDin8ANDin9);

ENDsop_arc;

13.用VHDL设计3-8译码器

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYdecoder_3_to_8IS

PORT(a,b,c,g1,g2a,g2b:

INSTD_LOGIC;

y:

OUTSTD_LOGIC_VECTOR(7downto0));

ENDdecoder_3_to_8;

ARCHITECTURErt1OFdecoder_3_to_8IS

SIGNALindata:

STD_LOGIC_VECTOR(2downto0);

BEGIN

indata<=c&b&a;

PROCESS(indata,g1,g2a,g2b)

BEGIN

IF(g1=′1′ANDg2a=′0′ANDg2b=′0′)THEN

CASEindataIS

WHEN"000"=>y<="11111110";

WHEN"001"=>y<="11111101";

WHEN"010"=>y<="11111011";

WHEN"011"=>y<="11110111";

WHEN"100"=>y<="11101111";

WHEN"101"=>y<="11011111";

WHEN"110"=>y<="10111111";

WHENothers=>y<="01111111";

ENDCASE;

ELSE

y<="11111111";

ENDIF;

ENDPROCESS;

ENDrt1;

14.用VHDL设计七段显示译码器

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYsegment7IS

PORT(xin:

INSTD_LOGIC_VECTOR(3downto0);

lt,rbi:

INSTD_LOGIC;

yout:

OUTSTD_LOGIC_VECTOR(6downto0);

birbo:

INOUTSTD_LOGIC);

ENDsegment7;

ARCHITECTUREseg7448OFsegment7IS

SIGNALsig_xin:

STD_LOGIC_VECTOR(3downto0);

BEGIN

sig_xin<=xin;

PROCESS(sig_xin,lt,rbi,birbo)

BEGIN

IF(birbo=′0′)THEN

yout<="0000000";

ELSIF(lt=′0′)THEN

yout<="1111111";

birbo<=′1′;

ELSIF(rbi=′0′ANDsig_xin="0000")THEN

yout<="0000000";

birbo<=′0′;

ELSIF(rbi=′1′ANDsig_xin="0000")THEN

yout<="1111110";

birbo<=′1′;

ELSE

birbo<=′1′;

CASEsig_xinIS

WHEN"0001"=>yout<="0110000";

WHEN"0010"=>yout<="1101101";

WHEN"0011"=>yout<="1111001";

WHEN"0100"=>yout<="0110011";

WHEN"0101"=>yout<="1011011";

WHEN"0110"=>yout<="0011111";

WHEN"0111"=>yout<="1110000";

WHEN"1000"=>yout<="1111111";

WHEN"1001"=>yout<="1110011";

WHENothers=>yout<="0100011";

ENDCASE;

ENDIF;

ENDPROCESS;

ENDseg7448;

15.用VHDL设计8/3优先编码器

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYpriorityencoderIS

PORT(din:

INSTD_LOGIC_VECTOR(7downto0);

ei:

INSTD_LOGIC;

yout:

OUTSTD_LOGIC_VECTOR(2downto0);

eo,gs:

OUTSTD_LOGIC);

ENDpriorityencoder;

ARCHITECTUREcod74148OFpriorityencoderIS

BEGIN

PROCESS(ei,din)

BEGIN

IF(ei=′1′)THEN

yout<="111";

eo<=′1′;

gs<=′1′;

ELSE

IF(din(7)=′0′)THEN

yout<="000";

eo<=′1′;

gs<=′0′;

ELSIF(din(6)=′0′)THEN

yout<="001";

eo<=′1′;

gs<=′0′;

ELSIF(din(5)=′0′)THEN

yout<="010";

eo<=′1′;

gs<=′0′;

ELSIF(din(4)=′0′)THEN

yout<="011";

eo<=′1′;

gs<=′0′;

ELSIF(din(3)=′0′)THEN

yout<="100";

eo<=′1′;

gs<=′0′;

ELSIF(din

(2)=′0′)THEN

yout<="101";

eo<=′1′;

gs<=′0′;

ELSIF(din

(1)=′0′)THEN

yout<="110";

eo<=′1′;

gs<=′0′;

ELSIF(din(0)=′0′)THEN

yout<="111";

eo<=′1′;

gs<=′0′;

ELSIF(din="11111111")THEN

yout<="111";

eo<=′0′;

gs<=′1′;

ENDIF;

ENDIF;

ENDPROCESS;

ENDcod74148;

16.用VHDL设计BCD码至二进制码转换器。

解:

源代码:

libraryieee;

useieee.std_logic_1164.all;

entitybcdtobiis

port(

bcdcode:

INSTD_LOGIC_VECTOR(7DOWNTO0);

start:

instd_logic;

qbit:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

);

end;

architecturebehavioralofbcdtobiis

begin

process(start)

begin

ifstart='0'then

casebcdcode(7downto0)is

when"00000000"=>qbit(3downto0)<="0000";

when"00000001"=>qbit(3downto0)<="0001";

when"00000010"=>qbit(3downto0)<="0010";

when"00000011"=>qbit(3downto0)<="0011";

when"00000100"=>qbit(3downto0)<="0100";

when"00000101"=>qbit(3downto0)<="0101";

when"00000110"=>qbit(3downto0)<="0110";

when"00000111"=>qbit(3downto0)<="0111";

when"00001000"=>qbit(3downto0)<="1000";

when"00001001"=>qbit(3downto0)<="1001";

when"00010000"=>qbit(3downto0)<="1010";

when"00010001"=>qbit(3downto0)<="1011";

when"00010010"=>qbit(3downto0)<="1100";

when"00010011"=>qbit(3downto0)<="1101";

when"00010100"=>qbit(3downto0)<="1110";

when"00010101"=>qbit(3downto0)<="1111";

whenothers=>qbit(3downto0)<="0000";

endcase;

else

qbit(3downto0)<="0000";

endif;

endprocess;

endbehavioral;

17.用VHDL设计4位寄存器

解:

异步复位

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYregister_4IS

PORT(clk,r:

INSTD_LOGIC;

din:

INSTD_LOGIC_VECTOR(3downto0);

qout:

OUTSTD_LOGIC_VECTOR(3downto0));

ENDregister_4;

ARCHITECTURErge_arcOFregister_4IS

SIGNALq_temp:

STD_LOGIC_VECTOR(3downto0);

BEGIN

PROCESS(clk,r)

BEGIN

IF(r=′1′)THEN

q_temp<="0000";

ELSIF(clk′eventANDclk=′1′)THEN

q_temp<=din;

ENDIF;

qout<=q_temp;

ENDPROCESS;

ENDrge_arc;

18.用VHDL设计4位双向移位寄存器

解:

s1、s0控制工作方式,dsl为左移数据输入,dsr为右移数据输入。

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYshiftregIS

PORT(clk,r,dsr,dsl:

INSTD_LOGIC;

s1,s0:

INSTD_LOGIC;--functionselect

din:

INSTD_LOGIC_VECTOR(3downto0);--datain

qout:

OUTSTD_LOGIC_VECTOR(3downto0));--dataout

ENDshiftreg;

ARCHITECTUREls74194OFshiftregIS

SIGNALiq:

STD_LOGIC_VECTOR(3downto0);

SIGNALs:

STD_LOGIC_VECTOR(1downto0);

BEGIN

s<=s1&s0;

PROCESS(clk,r)

BEGIN

IF(r=′0′)THEN

iq<="0000";

ELSIF(clk′eventANDclk=′1′)THEN

CASEsIS

WHEN"00"=>null;

WHEN"01"=>iq<=dsr&din(3downto1);--right

WHEN"10"=>iq<=din(2downto0)&dsl;--left

WHEN"11"=>iq<=din;--load

WHENothers=>null;

ENDCASE;

ENDIF;

qout<=iq;

ENDPROCESS;

ENDls74194;

19.用VHDL设计8421码十进制加法计数器

解:

异步清零,同步置数

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcount10IS

PORT(clk,clr,load:

INSTD_LOGIC;

din:

INSTD_LOGIC_VECTOR(3downto0);

co:

OUTSTD_LOGIC;

qout:

OUTSTD_LOGIC_VECTOR(3downto0));

ENDcount10;

ARCHITECTUREcount10_archOFcount10IS

SIGNALiq:

STD_LOGIC_VECTOR(3downto0);

BEGIN

PROCESS(clr,clk,load)

BEGIN

IF(clr=′0′)THEN

iq<="0000";

ELSIF(clk′eventANDclk=′1′)THEN

IF(load=′0′)THEN

iq<=din;

ELSIF(iq=9)THEN

iq<="0000";

ELSE

iq<=iq+1;

ENDIF;

ENDIF;

qout<=iq;

ENDPROCESS;

co<=′1′WHENiq="1001"ELSE

′0′;

ENDcount10_arch;

20.用VHDL设计可逆格雷码计数器

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYgray_countIS

PORT(clk,y:

INSTD_LOGIC;

qout:

OUTSTD_LOGIC_VECTOR(2downto0));

ENDgray_count;

ARCHITECTUREarch_grayOFgray_countIS

SIGNALiq:

STD_LOGIC_VECTOR(2downto0);

BEGIN

PROCESS(clk)

BEGIN

IF(clk′eventANDclk=′1′)THEN

IF(y=′1′)THEN

CASEiqIS

WHEN"000"=>iq<="001";

WHEN"001"=>iq<="011";

WHEN"011"=>iq<="010";

WHEN"010"=>iq<="110";

WHEN"110"=>iq<="111";

WHEN"111"=>iq<="101";

WHEN"101"=>iq<="100";

WHENothers=>iq<="000";

ENDCASE;

ENDIF;

IF(y=′0′)THEN

CASEiqIS

WHEN"000"=>iq<="100";

WHEN"100"=>iq<="101";

WHEN"101"=>iq<="111";

WHEN"111"=>iq<="110";

WHEN"110"=>iq<="010";

WHEN"010"=>iq<="011";

WHEN"011"=>iq<="001";

WHENothers=>iq<="000";

ENDCASE;

ENDIF;

ENDIF;

qout<=iq;

ENDPROCESS;

ENDarch_gray;

21.用VHDL设计有限状态机

解:

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYasmIS

PORT(clk,k,reset:

INSTD_LOGIC;

qout:

OUTSTD_LOGIC_VECTOR(1downto0));

ENDasm;

ARCHITECTUREasm_archOFasmIS

TYPEasm_stIS(s0,s1,s2,s3);

SIGNALcurrent_state,next_state:

asm_st;

BEGIN

reg:

PROCESS(clk,reset)

BEGIN

IF(reset=′1′)THEN

current_state<=s0;

ELSIF(clk′eventANDclk=′1′)THEN

current_state<=next_state;

ENDIF;

ENDPROCESS;

com:

PROCESS(current_state,k)

BEGIN

CASEcurrent_stateIS

WHENs0=>qout<="00";

IF(k=′0′)THEN

next_state<=s1;

ELSE

next_state<=s0;

ENDIF;

WHENs1=>qout<="01";

IF(k=′0′)THEN

next_state<=s1;

ELSE

next_state<=s2;

E

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 第五章 可编程逻辑 习题答案白中英主编第五版 第五 可编程 逻辑 习题 答案 英主

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx