数字逻辑第二版 华中科技大学出版社欧阳星明版数字逻辑答案第七章.docx

数字逻辑第二版 华中科技大学出版社欧阳星明版数字逻辑答案第七章.docx

- 文档编号:11523176

- 上传时间:2023-03-02

- 格式:DOCX

- 页数:14

- 大小:226.33KB

数字逻辑第二版 华中科技大学出版社欧阳星明版数字逻辑答案第七章.docx

《数字逻辑第二版 华中科技大学出版社欧阳星明版数字逻辑答案第七章.docx》由会员分享,可在线阅读,更多相关《数字逻辑第二版 华中科技大学出版社欧阳星明版数字逻辑答案第七章.docx(14页珍藏版)》请在冰豆网上搜索。

数字逻辑第二版华中科技大学出版社欧阳星明版数字逻辑答案第七章

习题七

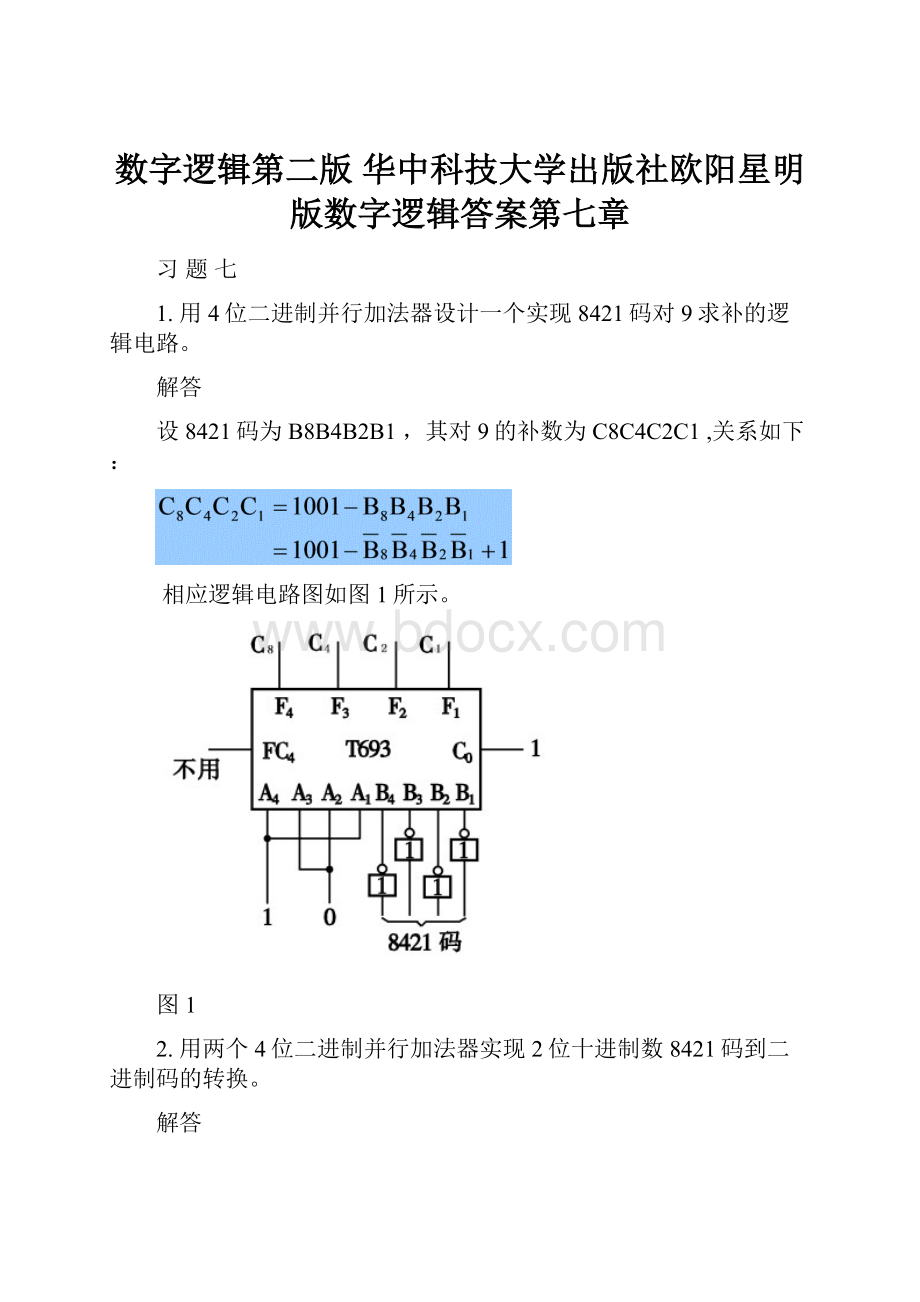

1.用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电路。

解答

设8421码为B8B4B2B1,其对9的补数为C8C4C2C1,关系如下:

相应逻辑电路图如图1所示。

图1

2.用两个4位二进制并行加法器实现2位十进制数8421码到二进制码的转换。

解答

设两位十进制数的8421码为D80D40D20D10D8D4D2D1,相应二进制数为B6B5B4B3B2B1B0,则应有B6B5B4B3B2B1B0=D80D40D20D10×1010+D8D4D2D1,运算如下:

×

D80

1

D40

0

D20

1

D10

0

+

D80

D40

D80

D20

D40

D10

D8

D20

D4

D10

D2

D1

B6

B5

B4

B3

B2

B1

B0

据此,可得到实现预定功能的逻辑电路如图2所示。

图2

3.用4位二进制并行加法器设计一个用8421码表示的1位十进制加法器。

解答

分析:

由于十进制数采用8421码,因此,二进制并行加法器输入被加数和加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也是8421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC4F4F3F2F1,修正后的结果为

,可列出修正函数真值表如表1所示。

表1

十进制数

输入

输出

修正控制

N

FC4

F4

F3

F2

F1

FC′

F′4

F′3

F′2

F′1

C

0

0

0

0

0

0

0

0

0

0

0

0

1

2

3

4

5

6

7

8

9

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

1

1

1

1

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

1

1

1

1

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

10

11

12

13

14

15

16

17

18

19

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

根据表1写出控制函数表达式,经简化后可得:

据此,可画出逻辑电路图如图3所示。

图3

4.用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

解答

假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:

逻辑电路图如图4所示。

图4

5.用一片4-16线译码器和适当的逻辑门设计一个1位十进制数2421码的奇偶位产生电路(假定采用奇检验)。

解答

设2421码为ABCD,奇偶检验位为P,根据题意可列出真值表如表2所示。

表2

ABCD

P

ABCD

P

0000

0001

0010

0011

0100

1

0

0

1

0

1011

1100

1101

1110

1111

0

1

0

0

1

由真值表可得:

假定采用74LS154和与非门实现给定函数功能,可画出逻辑电路图如图5所示。

图5

6.当优先编码器74LS148的Is接0,输入I7I6I5I4I3I2I1I0=11010001时,输出为什么状态?

解答

QCQBQA=010(编码I5),QEX=0(编码群输出端,允许编码且有信号输入时为0),QS=1(允许输出端,允许编码且有信号输入时为1)。

7.试用4路数据选择器实现余3码到8421码的转换。

解答

假定用ABCD表示余3码,WXYZ表示8421码,并选择A、B作为选择变量,可求出各4路数据选择器的数据输入端分别为:

用4个四路数据选择器和4个逻辑门构造出该代码转换电路,逻辑图如图6所示。

图6

8.当4路选择器的选择控制变量A1、A0接变量A、B,数据输入端D0、D1、D2、D3依次接

、0、0、C时,电路实现何功能?

解答

输出函数表达式如下:

电路实现三变量“一致性”检测功能。

9.用4位二进制同步可逆计数器T4193和必要的逻辑门实现模12加法计数器。

解答

根据T4193的逻辑功能,可画出模12加法计数器的逻辑电路图如图7所示。

图7

10.用T1194双向移位寄存器和必要的逻辑门设计一个00011101序列信号发生器。

解答

设寄存器初始状态Q0Q1Q2=101,从Q2产生输出,可列出反馈函数真值表如表3所示。

表3

CP

Q0Q1Q2

F(DR)

0

1

2

3

4

5

6

7

101

110

111

011

001

000

100

010

1

1

0

0

0

1

0

1

由表3可写出反馈函数表达式:

设计出该序列发生器的逻辑电路图如图8所示。

图8

11.在图9所示电路中,若取R1=2R2,请问输出矩形波的占空比为多少?

图9

解答

12.分析图10所示由定时器5G555构成的多谐振荡器。

图10

(1)计算其振荡周期;

(2)若要产生占空比为50%的方波,R1和R2的取值关系如何?

解答

(1)振荡周期:

(2)占空比:

要产生占空比为50%的方波,应有R1=R2。

13.将5G555定时器按图11(a)所示连接,输入波形如图11(b)所示。

请画出定时器输出波形,并说明该电路相当于什么器件。

图115G555连线图和有关波形图

解答

假定电路的初始输出为高,可画出输出波形如图12所示。

图12

由输入输出波形图可知,该电路的功能相当于一个基本R-S触发器。

14.D/A转换器有哪些主要参数?

通常用什么参数来衡量转换精度?

解答

D/A转换器的主要参数有分辨率、非线性误差、绝对精度、建立时间。

通常用分辨率衡量转换精度。

15.DAC1210是12位D/A芯片,请问其分辨率为多少?

(用百分数表示)解答

分辨率=

16.DAC0832由哪几部分组成?

可以构成哪几种工作方式?

每种方式如何控制?

解答

DAC0832由两个8位数据缓冲寄存器、一个8位D/A转换器和三个控制逻辑门组成,可以构成双缓冲、单缓冲和直通三种工作方式。

工作方式选择受控制信号

的控制。

双缓冲方式:

首先在

控制下将数据锁存到输入寄存器,然后在

控制下将输入寄存器中数据锁存到DAC寄存器。

单缓冲方式:

令输入寄存器和DAC寄存器中的一个处于受控状态,另一个处于直通状态。

直通方式:

令输入寄存器和DAC寄存器中均处于直通状态。

17.常见集成A/D转换器按转换方法的不同可分成哪几种类型?

各有何特点?

解答

集成A/D转换器按转换方法的不同可分成并行比较型、逐次比较型和双积分型几种类型。

并行比较型转换速度高,但由于内部线路较复杂,一般分辨率较低;逐次比较型速度较快,精度高;双积分型精度高、抗干扰能力强,但速度较慢。

18.ADC0809如何实现对8路模拟量输入的选择?

当它与微机连接时是否要外加三态缓冲器?

解答

ADC0809由3根地址选择线实现对8路模拟量输入的选择。

由于ADC0809内部带有三态输出缓冲器,所以当它与微机连接时不需要外加三态缓冲器。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字逻辑第二版 华中科技大学出版社欧阳星明版数字逻辑答案第七章 数字 逻辑 第二 华中科技大学 出版社 欧阳 星明版 答案 第七

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx