C51单片机汇编语言指令集.docx

C51单片机汇编语言指令集.docx

- 文档编号:10744161

- 上传时间:2023-02-22

- 格式:DOCX

- 页数:23

- 大小:199.28KB

C51单片机汇编语言指令集.docx

《C51单片机汇编语言指令集.docx》由会员分享,可在线阅读,更多相关《C51单片机汇编语言指令集.docx(23页珍藏版)》请在冰豆网上搜索。

C51单片机汇编语言指令集

C51单片机汇编语言指令集

51汇编语言指令集

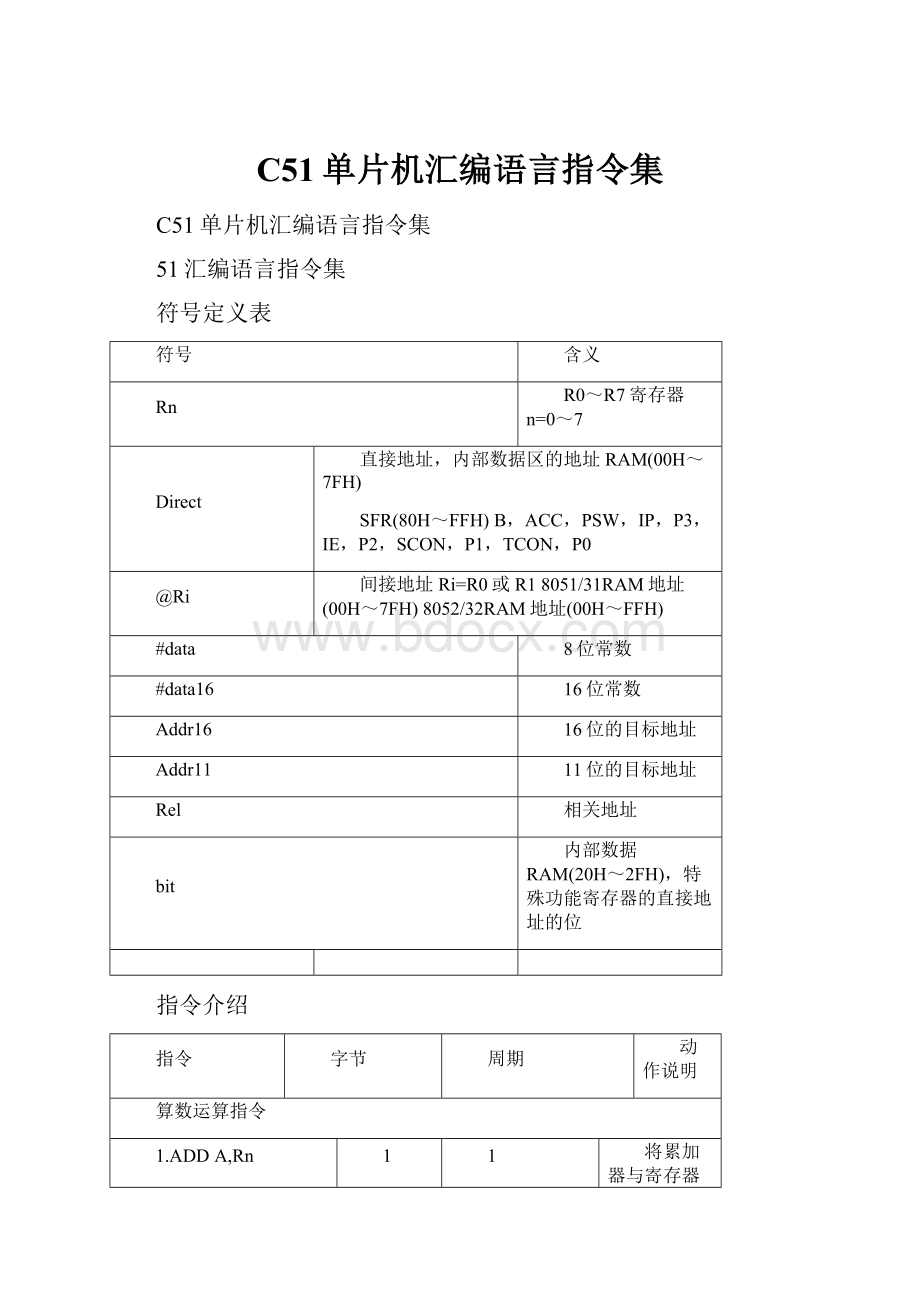

符号定义表

符号

含义

Rn

R0~R7寄存器n=0~7

Direct

直接地址,内部数据区的地址RAM(00H~7FH)

SFR(80H~FFH)B,ACC,PSW,IP,P3,IE,P2,SCON,P1,TCON,P0

@Ri

间接地址Ri=R0或R18051/31RAM地址(00H~7FH)8052/32RAM地址(00H~FFH)

#data

8位常数

#data16

16位常数

Addr16

16位的目标地址

Addr11

11位的目标地址

Rel

相关地址

bit

内部数据RAM(20H~2FH),特殊功能寄存器的直接地址的位

指令介绍

指令

字节

周期

动作说明

算数运算指令

1.ADDA,Rn

1

1

将累加器与寄存器的内容相加,结果存回累加器

2.ADDA,direct

2

1

将累加器与直接地址的内容相加,结果存回累加器

3.ADDA,@Ri

1

1

将累加器与间接地址的内容相加,结果存回累加器

4.ADDA,#data

2

1

将累加器与常数相加,结果存回累加器

5.ADDCA,Rn

1

1

将累加器与寄存器的内容及进位C相加,结果存回累加器

6.ADDCA,direct

2

1

将累加器与直接地址的内容及进位C相加,结果存回累加器

7.ADDCA,@Ri

1

1

将累加器与间接地址的内容及进位C相加,结果存回累加器

8.ADDCA,#data

2

1

将累加器与常数及进位C相加,结果存回累加器

9.SUBBA,Rn

1

1

将累加器的值减去寄存器的值减借位C,结果存回累加器

10.SUBBA,direct

2

1

将累加器的值减直接地址的值减借位C,结果存回累加器

11.SUBBA,@Ri

1

1

将累加器的值减间接地址的值减借位C,结果存回累加器

12.SUBBA,0data

2

1

将累加器的值减常数值减借位C,结果存回累加器

13.INCA

1

1

将累加器的值加1

14.INCRn

1

1

将寄存器的值加l

15.INCdirect

2

1

将直接地址的内容加1

16.INC@Ri

1

1

将间接地址的内容加1

17.INCDPTR

1

1

数据指针寄存器值加1

说明:

将16位的DPTR加1,当DPTR的低字节(DPL)从FFH溢出至00H时,会使高字节(DPH)加1,不影响任何标志位

18.DECA

1

1

将累加器的值减1

19.DECRn

1

1

将寄存器的值减1

20.DECdirect

2

1

将直接地址的内容减1

21.DEC@Ri

1

1

将间接地址的内容减1

22.MULAB

1

4

将累加器的值与B寄存器的值相乘,乘积的低位字节存回累加器,高位字节存回B寄存器

说明:

将累加器A和寄存器B内的无符号整数相乘,产生16位的积,低位字节存入A,高位字节存入B寄存器。

如果积大于FFH,则溢出标志位(OV)被设定为1,而进位标志位为0

23.DIVAB

1

4

将累加器的值除以B寄存器的值,结果的商存回累加器,余数存回B寄存器

说明:

无符号的除法运算,将累加器A除以B寄存器的值,商存入A,余数存入B。

执行本指令后,进位位(C)及溢出位(OV)被清除为0

24.DAA

1

1

将累加器A作十进制调整,

若(A)3-0>9或(AC)=1,则(A)3-0←(A)3-0+6

若(A)7-4>9或(C)=1,则(A)7-4←(A)7-4+6

逻辑运算指令

ANLA,Rn

1

1

将累加器的值与寄存器的值做AND的逻辑判断,结果存回累加器

ANLA,direct

2

1

将累加器的值与直接地址的内容做AND的逻辑判断,结果存回累加器

ANLA,@Ri

1

1

将累加器的值与间接地址的内容做AND的逻辑判断,结果存回累加器

ANLA,#data

2

1

将累加器的值与常数做AND的逻辑判断,结果存回累加器

ANLdirect,A

2

1

将直接地址的内容与累加器的值做AND的逻辑判断,结果存回该直接地址

ANLdirect,#data

3

2

将直接地址的内容与常数值做AND的逻辑判断,结果存回该直接地址

ORLA,Rn

1

1

将累加器的值与寄存器的值做OR的逻辑判断,结果存回累加器

32.ORLA,direct

2

1

将累加器的值与直接地址的内容做OR的逻辑判断,结果存回累加器

33.ORLA,@Ri

1

1

将累加器的值与间接地址的内容做OR的逻辑判断,结果存回累加器

34.ORLA,#data

2

1

将累加器的值与常数做OR的逻辑判断,结果存回累加器

35.ORLdirect,A

2

1

将直接地址的内容与累加器的值做OR的逻辑判断,结果存回该直接地址

36.ORLdirect,#data

3

2

将直接地址的内容与常数值做OR的逻辑判断,结果存回该直接地址

37.XRLA,Rn

1

1

将累加器的值与寄存器的值做XOR的逻辑判断,结果存回累加器

38.XRLA,direct

2

1

将累加器的值与直接地址的内容做XOR的逻辑判断,结果存回累加器

39.XRLA,@Ri

1

1

将累加器的值与间接地扯的内容做XOR的逻辑判断,结果存回累加器

40.XRLA,#data

2

1

将累加器的值与常数作XOR的逻辑判断,结果存回累加器

XRLdirect,A

2

1

将直接地址的内容与累加器的值做XOR的逻辑判断,结果存回该直接地址

42.XRLdirect,#data

3

2

将直接地址的内容与常数的值做XOR的逻辑判断,结果存回该直接地址

43.CLRA

1

1

清除累加器的值为0

44.CPLA

1

1

将累加器的值反相

45.RLA

1

1

将累加器的值左移一位

46.RLCA

1

1

将累加器含进位C左移一位

47.RRA

1

1

将累加器的值右移一位

48.RRCA

1

1

将累加器含进位C右移一位

49.SWAPA

1

1

将累加器的高4位与低4位的内容交换。

(A)3-0←(A)7-4

数据转移指令

50.MOVA,Rn

1

1

将寄存器的内容载入累加器

51.MOVA,direct

2

1

将直接地址的内容载入累加器

52.MOVA,@Ri

1

1

将间接地址的内容载入累加器

53.MOVA,#data

2

1

将常数载入累加器

54.MOVRn,A

1

1

将累加器的内容载入寄存器

55.MOVRn,direct

2

2

将直接地址的内容载入寄存器

56.MOVRn,gdata

2

1

将常数载入寄存器

57.MOVdirect,A

2

1

将累加器的内容存入直接地址

58.MOVdirect,Rn

2

2

将寄存器的内容存入直接地址

59.MOVdirect1,direct2

3

2

将直接地址2的内容存入直接地址1

60.MOVdirect,@Ri

2

2

将间接地址的内容存入直接地址

61.MOVdirect,#data

3

2

将常数存入直接地址

62.MOV@Ri,A

1

1

将累加器的内容存入某间接地址

63.MOV@Ri,direct

2

2

将直接地址的内容存入某间接地址

64.MOV@Ri,#data

2

1

将常数存入某间接地址

65.MOVDPTR,#data16

3

2

将16位的常数存入数据指针寄存器

66.MOVCA,@A+DPTR

1

2

(A)←((A)+(DPTR))

累加器的值再加数据指针寄存器的值为其所指定地址,将该地址的内容读入累加器

67.MOVCA,@A+PC

1

2

(PC)←(PC)+1;(A)←((A)+(PC))累加器的值加程序计数器的值作为其所指定地址,将该地址的内容读入累加器

68.MOVXA,@Ri

1

2

将间接地址所指定外部存储器的内容读入累加器(8位地址)

69.MOVXA,@DPTR

1

2

将数据指针所指定外部存储器的内容读入累加器(16位地址)

70.MOVX@Ri,A

1

2

将累加器的内容写入间接地址所指定的外部存储器(8位地址)

71.MOVX@DPTR,A

1

2

将累加器的内容写入数据指针所指定的外部存储器(16位地址)

72.PUSHdirect

2

2

将直接地址的内容压入堆栈区

73.POPdirect

2

2

从堆栈弹出该直接地址的内容

74.XCHA,Rn

1

1

将累加器的内容与寄存器的内容互换

75.XCHA,direct

2

1

将累加器的值与直接地址的内容互换

76.XCHA,@Ri

1

1

将累加器的值与间接地址的内容互换

77.XCHDA,@Ri

1

1

将累加器的低4位与间接地址的低4位互换

布尔代数运算

78.CLRC

1

1

清除进位C为0

79.CLRbit

2

1

清除直接地址的某位为0

80.SETBC

1

1

设定进位C为1

81.SETBbit

2

1

设定直接地址的某位为1

82.CPLC

1

1

将进位C的值反相

83.CPLbit

2

1

将直接地址的某位值反相

84.ANLC,bit

2

2

将进位C与直接地址的某位做AND的逻辑判断,结果存回进位C

85.ANLC,/bit

2

2

将进位C与直接地址的某位的反相值做AND的逻辑判断,结果存回进位C

86.ORLC,bit

2

2

将进位C与直接地址的某位做OR的逻辑判断,结果存回进位C

87.ORLC,/bit

2

2

将进位C与直接地址的某位的反相值做OR的逻辑判断,结果存回进位C

88.MOVC,bit

2

1

将直接地址的某位值存入进位C

89.MOVbit,C

2

2

将进位C的值存入直接地址的某位

90.JCrel

2

2

若进位C=1则跳至rel的相关地址

91.JNCrel

2

2

若进位C=0则跳至rel的相关地址

92.JBbit,rel

3

2

若直接地址的某位为1,则跳至rel的相关地址

93.JNBbit,rel

3

2

若直接地址的某位为0,则跳至rel的相关地址

94.JBCbit,rel

3

2

若直接地址的某位为1,则跳至rel的相关地址,并将该位值清除为0

程序跳跃

95.ACALLaddr11

2

2

调用2K程序存储器范围内的子程序

96.LCALLaddr16

3

2

调用64K程序存储器范围内的子程序

97.RET

1

2

从子程序返回

98.RETI

1

2

从中断子程序返回

99.AJMPaddr11

2

2

绝对跳跃(2K内)

100.LJMPaddr16

3

2

长跳跃(64K内)

101.SJMPrel

2

2

短跳跃(2K内)-128~+127字节

102.JMP@A+DPTR

1

2

跳至累加器的内容加数据指针所指的相关地址

103.JZrel

2

2

累加器的内容为0,则跳至rel所指相关地址

104.JNZrel

2

2

累加器的内容不为0,则跳至rel所指相关地址

105.CJNEA,direct,rel

3

2

将累加器的内容与直接地址的内容比较,不相等则跳至rel所指的相关地址

106.CJNEA,#data,rel

3

2

将累加器的内容与常数比较,若不相等则跳至rel所指的相关地址

CJNE@Rn,#data,rel

3

2

将寄存器的内容与常数比较,若不相等则跳至rel所指的相关地址

CJNE@Ri,#data,rel

3

2

将间接地址的内容与常数比较,若不相等则跳至rel所指的相关地址

109.DJNZRn,rel

2

2

将寄存器的内容减1,不等于0则跳至rel所指的相关地址

110.DJNZdirect,rel

3

2

将直接地址的内容减1,不等于0则跳至rel所指的相关地址

111.NOP

1

1

无动作

符号

地址

功能介绍

B

F0H

B寄存器

ACC

E0H

累加器

PSW

D0H

程序状态字

IP

B8H

中断优先级控制寄存器

P3

B0H

P3口锁存器

IE

A8H

中断允许控制寄存器

P2

A0H

P2口锁存器

SBUF

99H

串行口锁存器

SCON

98H

串行口控制寄存器

P1

90H

P1口锁存器

TH1

8DH

定时器/计数器1(高8位)

TH0

8CH

定时器/计数器1(低8位)

TL1

8BH

定时器/计数器0(高8位)

TL0

8AH

定时器/计数器0(低8位)

TMOD

89A

定时器/计数器方式控制寄存器

TCON

88H

定时器/计数器控制寄存器

DPH

83H

数据地址指针(高8位)

DPL

82H

数据地址指针(低8位)

SP

81H

堆栈指针

P0

80H

P0口锁存器

PCON

87H

电源控制寄存器

P3.0

RXD

串行口输入端

P3.1

TXD

串行口输出端

P3.2

INT0

外部中断0请求输入端,低电平有效

P3.3

INT1

外部中断1请求输入端,低电平有效

P3.4

T0

定时器/计数器0计数脉冲输入端

P3.5

T1

定时器/计数器1计数脉冲输入端

P3.6

WR

外部数据存储器写选通信号输出端,低电平有效

P3.7

RD

外部数据存储器读选通信号输出端,低电平有效

CY(PSW.7)——进位标志位。

AC(PSW.6)——辅助进位(或称半进位)标志。

F0(PSW.5)——由用户定义的标志位。

RS1(PSW.4)、RS0(PSW.3)——工作寄存器组选择位。

OV(PSW.2)——溢出标志位。

由硬件置位或清零。

PSW.1——未定义位。

P(PSW.0)——奇偶标志位。

位寻址区

20H~2FH单元是位寻址区。

这16个单元(共计16×8=128位)的每一位都赋予了一个位地址,位地址范围为00H~7FH。

位寻址区的每一位都可当作软件触发器,由程序直接进行位处理。

通常可以把各种程序状态标志、位控制变量存于位寻址区内。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- C51 单片机 汇编语言 指令

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx