FPGA.docx

FPGA.docx

- 文档编号:10540914

- 上传时间:2023-02-21

- 格式:DOCX

- 页数:20

- 大小:400.31KB

FPGA.docx

《FPGA.docx》由会员分享,可在线阅读,更多相关《FPGA.docx(20页珍藏版)》请在冰豆网上搜索。

FPGA

基于FPGA的移位寄存器流水线结构FFT处理器设计与实现

技术分类:

可编程器件 |2010-07-19

现代电子技术郝小龙韦高刘娜

0引言

快速傅里叶变换(FFT)在雷达、通信和电子对抗等领域有广泛应用。

近年来现场可编程门阵列(FPGA)的飞速发展,与DSP技术相比,由于其并行信号处理结构,使得FPGA能够很好地适用于高速信号处理系统。

由于Altera等公司研制的FFTIP核,价钱昂贵,不适合大规模应用,在特定领域中,设计适合于自己领域需要的FFT处理器是较为实际的选择。

本文设计的FFT处理器,基于FPGA技术,由于采用移位寄存器流水线结构,实现了两路数据的同时输入,相比传统的级联结构,提高了蝶形运算单元的运算效率,减小了输出延时,降低了芯片资源的使用。

在OFDM系统的实际应用中,因它可以采用快速傅里叶变换,能方便快捷地实现调制和解调,故结合MIMO技术,设计的FFT处理器结构,可以很好地应用于2根天线的MIMO-OFDM系统中。

1FFT处理的应用及DIFFFT算法原理

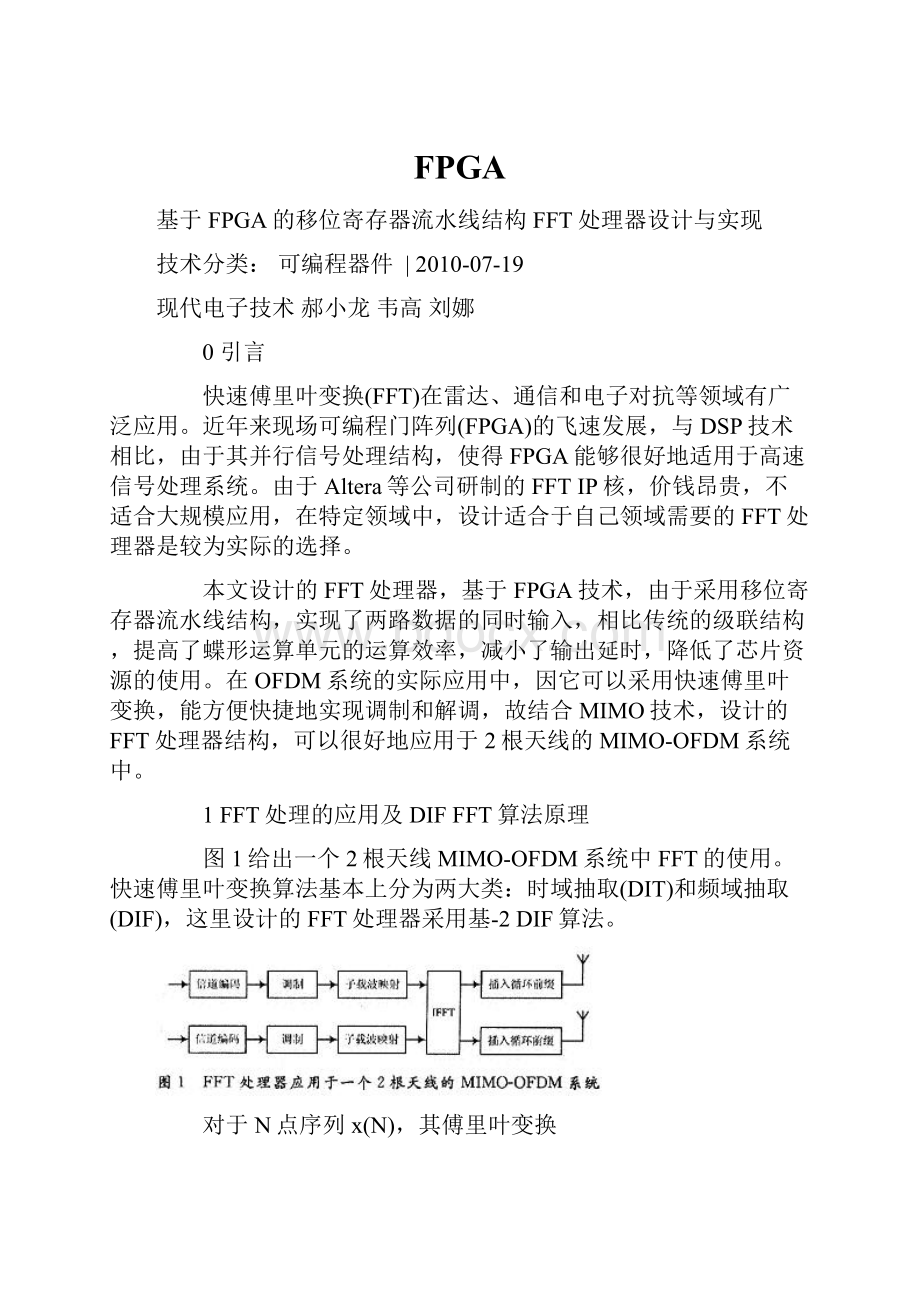

图1给出一个2根天线MIMO-OFDM系统中FFT的使用。

快速傅里叶变换算法基本上分为两大类:

时域抽取(DIT)和频域抽取(DIF),这里设计的FFT处理器采用基-2DIF算法。

对于N点序列x(N),其傅里叶变换

将x(n)分成上、下两部分,得:

这样将两个N点的DFT分成两个N/2点的DFT,分的方法是将x(k)按序号k的奇、偶分开。

通过这种方式继续分下去,直到得到两点的DFT。

采用DIF方法设计的FFT,其输入是正序,输出是按照奇偶分开的倒序。

2移位寄存器流水线结构的FFT

在传统流水线结构的FFT中,需要将全部数据输入寄存器后,可开始蝶形运算。

在基-2DIF算法中可以发现,当前N/2个数据进入寄存器后,运算便可以开始,此后进入的第N/2+1个数据与寄存器第一个数据进行蝶形运算,以此类推。

由于采用频域抽取法,不需要对输入的数据进行倒序处理,简化了地址控制,这样,可以采用移位寄存器的方式,依次将前N/2个数据移入移位寄存器,在N/2+l时刻,第一个数据移出移位寄存器,参与运算。

相对于传统的RAM读写方式,采用移位寄存器存储结构综合后的最大工作频率为500MHz,远大于RAM方式的166MHz。

当移位寄存器相继有数据移出时,在移位寄存器中会出现空白位。

此时,引入第二路数据,在第一路数据依次移出进行蝶算时,第二路数据依次补充到移位寄存器的空白位中,为运算做准备。

通过这样一种类似“乒乓操作”的结构,可以使蝶形运算模块中的数据不间断地输入,运算效率达到100%。

不同于传统的“乒乓操作”结构,由于使用移位寄存器,不需要两块RAM,可以省掉一半的寄存器。

图2为256点FFT处理器的第一级结构。

基于上述基本原理,将这种移位寄存器结构扩展到整个FFT系统的各级,可以发现各级使用的移位寄存器数量是递减的。

现使用一个8点结构来进行说明。

如图3所示,数据由输入l和输入2进入第一级。

通过开关进行选通控制。

由于是N=8的运算,所以各级分别加入4级、2级和1级的移位寄存器。

分两路来说明运算过程:

将K1打到位置①,第一路数据进入移位寄存器,待第一路的前4个数据存入4级移位寄存器后,第一路进入的第5个数据与移位寄存器移出的第1个数据进行蝶形运算。

由于输出结果有上下两路,第二级是一个四点的DFT,所以对于上路的输出结果x0(0)+x0(4)类似于第一级,直接存入下一级寄存器,为四点运算做准备,下路的输出,

先存入本级2级移位寄存器中,等到上路的四点运算开始,第二级的移位寄存器有空白位时,移入第二级,为下路的四点运算做准备。

所以第一级蝶形运算上路输出前N/4=2个进入下一级寄存器,下路输出的数据依次存入本级移位寄存器中。

当第一级的输出前N/4=2个数据x0(0)+x0(4)和x0

(1)+x0(5)存入第二级移位寄存器时,运算便可以开始,这时开关K2打到位置②,此时第一级上路输出的数据x0

(2)+x0(6),即第一级上路输出的第三个数据与第二级移位寄存器移出的第一个数据,即x0(O)+x0(4)进行蝶形运算,输出的第四个数据x0(3)+x0(7)与x0

(1)+x0(5)进行蝶算。

在这个运算过程中,第一级的2级移位寄存器移出数据依次移位存入到第二级的移位寄存器产生的空白位中。

两个时钟后,第一级上路输出的四个数据完成了蝶形运算,K2打到位置①,在接下来的两个时钟里,第一级中2级移位寄存器的输出依次与此时第二级中2级移位寄存器的输出数据进行蝶形运算,即

与

,

与

完成第一级下路输出的四个数据的蝶形运算。

此时,第一路在第一级运算后的输出数据,在第二级完成了全部的蝶形运算。

第二级的输出结果同第一级一样,蝶形运算的上路输出前N/8=1个进入下一级寄存器,后一个数据直接进入后一级进行碟算,下路输出的数据存入本级移位寄存器中。

第三级的运算与第二级和第一级类似,即移入1级寄存器的数据与其后一个数据进行碟算,同时使前一级寄存器的输出数据进入后一级寄存器的空白位中,然后开关打到位置②,对下路输出数据进行碟算。

对于第二路数据,通过开关控制,在第二级中,待第一路第一级下路输出数据进行蝶形运算时,移入寄存器的空白位,为运算做准备,由于前级运算周期是后级运周期的两倍,对于第二级碟算模块而言,数据仍然是不间断输入的。

通过这样两路数据的交替运算和存储,实现“乒乓操作”,从而提高了蝶形运算模块的运算效率。

图4是256点FFT的具体运算输入和输出时序图。

对于只有一路数据的应用场合,可以在前级加入,门控开关和数据缓冲寄存器分成两路数据,实现一路数据的不间断读入。

由于采用移位寄存器结梅,各级寄存器使用的数量都是固定的,即为N/2+N/4。

其中,N为该级DFT运算的点数,各级使用的移位寄存器深度逐级递减,从而大大降低了寄存器的使用数量。

此外,由于各级结构固定,所以大点数FFT只是小点数FFT基础上级数的增加,而且由于移位寄存器的输出相对于RAM而言不需要复杂的地址控制,所以这种结构的FFT处理器具有非常好的可扩展性。

比如需要实现512点的FFT,只需要在256点的基础上增加一级即可。

基于DSP的低功耗接收机单边带解调方法

技术分类:

通信 微处理器与DSP |2007-03-05

来源:

现代电子技术|张铭敏 张立国等

1数字前端

该低功耗数字接收机主要是针对语音信号的,要处理的信号都是窄带的。

对数字前端中的混频器送出的模拟窄带中频信号进行采样,产生数字窄带中频信号。

对该信号进行解调之前,先将频谱搬至零中频处,再进行滤波,降采样率等处理,如图1所示。

图1中A/D表示模数转换器,LPF表示低通滤波器,fs表示采样率,fo表示最靠近零频处镜像的中频。

其中LPF实现如图2所示的功能。

设滤出的复数信号采样率降为f's=fs/M。

图2中,细线表示上边带(USB),粗线表示下边带(LSB)。

说明一点,在实际中,上下边带的位置关系要根据模拟信号的中频及采样率fs才能确定,这里为了方便解释,就认为LSB在左,USB在右。

2解调方案一

以解调上边带为例,如图3所示,设计一个数字带通滤波器,其频响关于中心频率fo'对称,

别为f3,f4,截止频率处的衰减至少为-20dB。

该带通滤波器的设计步骤如下:

(1)先设计一个低

通滤波器,通带带宽为Δf1=f2-f1,过渡带带宽为Δf2=f1-f3。

估算滤波器阶数:

N=

(2)将上述的低通滤波器进行频谱搬移即可实现该带通滤波器(BPF),如图5所示。

因此滤波器系数:

(3)如果利用FIRS指令实现边带滤波器,那么边带滤波的执行时间会降为原来的一半。

但这时要求滤波器的系数是对称的。

前面提到的低通滤波器系数是对称的。

为使带通滤波器的系数对称,我们将带通滤波器的系数附加一个相位△φ(n)。

即:

的实部和虚部均为正。

所以,带通滤波器的系数有这样的特点:

实部偶对称,虚部奇对称。

3解调方案二

还是以解调上边带为例,先搬移待解调信号的频谱,再做低通滤波,最后又将信号的频谱搬移回来,如图7所示。

这种方案滤波器的设计思路简单,但要对信号进行两次频谱搬移。

LPF与方案一中所设计的低通滤波器相同。

如图8所示,信号被搬至零中频处。

4两种方案的比较

方案一中,带通滤波器在一个时钟周期内进行如下的计算:

其中"*"表示卷积运算,下同。

这表示要做4N次乘加运算,考虑到对称性只需要2N次乘加运算。

如果信号不是独立边带的,上边带信号解调所用的带通滤波器的系数与下边带信号解调所用的带通滤波器的系数是共轭关系,即hUSB(n)=hLSB*(n),则另外一个边带的滤波计算为:

其结果与前面的成共轭关系,因此,只要得到其中一个边带的实数部分即可得到解调结果。

这样只需要N次乘加运算。

如果是独立边带的,上下边带的共轭关系不存在,则解调其中一个边带需要2N次乘加运算,上下边带解调共需要4N次乘加运算。

方案二中,低通滤波器在一个时钟周期内进行如下的计算:

这表示要做2N次乘加运算,考虑到对称性只需要N次乘加运算。

如果信号不是独立边带的,那么同方案一,只需要N/2次乘加运算。

如果信号是独立边带的那就上下边带解调共需要2N次乘加运算。

另外两次经过NCO的运算在一个时钟周期内共需要8次乘加运算。

综合来说,就运算开销方面而言方案二要优于方案一。

转贴:

FPGA开发的十点经验

文章发表于:

2010-05-2919:

34

1、FPGA器件选型的7个原则:

器件供货渠道和开发工具的支持、器件的硬件资源、器件的电气接口标准、器件的速度等级、器件的稳定等级、器件的封装和器件的价格。

2、Spartan-3E和Spartan-3A主要运用于逻辑设计和简单数字信号处理,Virtex-4LX和Virtex-5LX主要用于高速逻辑运算,Virtex-4SX和Virtex-5SX主要用于高速复杂数字信号处理,Virtex-4FX和Virtex-5FX主要用于嵌入式系统。

3、硬件资源包括:

逻辑资源、I/0口资源、布线资源、DSP资源、存储器资源、锁相环资源、串行收发器资源和硬核微处理器资源等。

4、过度I/O口资源的消耗可能会导致2个问题:

FPGA负荷过重,器件发热严重,严重影响器件的速度性能、工作稳定度和寿命,设计中要考虑器件的散热问题;局部布线资源不足,电路的运行速度明显降低,有时甚至使设计不能适配器件,设计失败。

5、器件中存储器资源主要有2个用途:

作高性能滤波器;实现小容量高速数据缓存。

6、面积优先原则可以节省器件内部的逻辑资源,尽可能地使用串行逻辑结构,但是以牺牲速度为代价;而速度优先原则保证了器件的整体工作速度,即尽可能地使用并行逻辑结构,但是以牺牲逻辑资源为代价。

7、添加约束的原则为先附加全局约束,再补充局部约束,而且局部约束比较宽松。

其目的是在可能的地方尽量放松约束,提高布线成功概率,减少ISE布局布线时间。

典型的全局约束包括周期约束和偏移约束。

8、在添加全局时序约束时,需要根据时钟频率划分不同的时钟域,添加各自的周期约束;然后对输入输出端口信号添加偏移约束,对片内逻辑添加附加约束。

9、附加时钟周期约束的两种方法:

简易方法和推荐方法。

简易方式是直接将周期约束附加到寄存器时钟网线上,其语法为:

[约束信号]PERIOD={周期长度}{HIGH|LOW}[脉冲持续时间];其中[]内的内容为可选项,{}中的内容为必选项,“|”表示选择项。

如:

Net"clk_100MHz"period=10nsHigh5ns。

推荐方法常用于约束具有复杂派生关系的时钟网络,其语法为:

TIMESPEC"TS_identifier"=PERIOD"TNM_reference"{周期长度}{HIGH|LOW}[脉冲持续时间]。

如:

NET"clk_50MHz"="syn_clk";TIMESPECT"TS_sync_clk"=PERIOD"sync_clk"20HIGH10。

TIMESPEC利用识别符定义派生时钟的语法为:

TIMESPEC"TS_identifier2"=PERIOD"timegroup_name""TS_identifier1"[*|/]倍数因子[+|-]phasevalue[单位]。

(详见FPGA开发全攻略第45页)。

10、造成时序性能差的直接原因可分为三类:

布局较差、逻辑级数过多以及信号扇出过高。

28nmFPGA实现高带宽、低功耗和低成本

技术分类:

可编程器件 |2010-05-30

陆楠,EDNChina执行主编

高端系统如通信、广播、军事、计算机存储等,对带宽的要求越来越高,人们希望在不改变引脚的情况下,以相同甚至更低的功耗来实现更大的带宽,而成本要求越低越好,至少在目前,摩尔定律还是能够推动和支持这一需求的方法。

不久前,Altera正式发布了他们的下一代28nmStraTIxVFPGA,这也是目前拥有最高带宽的FPGA。

据Altera亚太区资深市场经理罗嘉鸾介绍,StratixVFPGA具有1.6Tbps串行交换能力,采用28nm工艺,降低了宽带应用的成本和功耗。

较40nm的StratixIV集成的11.3Gbps收发器,StratixV拥有多达66个高速嵌入式收发器,大大提高了密度并降低了成本,新器件具有集成嵌入式HardCopy模块,部分重配置支持不断电重复设计等特性。

罗嘉鸾表示,StratixV采用TSMC28nm高性能(HP)工艺制造,其性能比其他28nm工艺高35%,功耗比StratixIV低30%。

StratixV有110万逻辑单元(LE)、53Mbits嵌入式存储器、3,680个18x18乘法器,以及工作在业界最高速率28Gbps的集成收发器。

新器件还采用了业界顶级的专用硬核IP,在不增加成本和功耗的前提下提高了系统集成度和性能。

针对无线/固网通信、广播、计算机和存储、测试和医疗市场的多种应用需求,StratixV推出四种型号:

StratixVGT是业界唯一面向100G以上系统,集成28Gbps收发器的FPGA;StratixVGX集成支持多种应用的600Mbps~12.5Gbps收发器;StratixVGS适用于高性能数字信号处理(DSP)应用,同样集成了600Mbps~12.5Gbps收发器;StratixVE则是适用于ASIC原型开发和仿真以及高性能计算应用的高密度FPGA。

罗嘉鸾强调,StratixV在带宽方面做了很大提升,StratixVGX和StratixVGS含有66个高性能、低功耗12.5Gbps收发器;StratixVGT的28Gbps收发器设计用于满足CEI28G规范。

28Gbps收发器每通道功耗只有200mW,大幅度降低了系统单位带宽功耗。

并且由于提高了单个收发器速度,所以整个FPGA虽然缩小但并没增加I/O口的负担。

StratixV支持多种3G、6G和10G协议以及电气标准,满足兼容性要求,例如,10G/40G/100G、Interlaken和PCIExpressGen3、Gen2和Gen1。

该器件还支持与10G背板(10GBASE-KR)和光模块的直接链接。

另外,除了收发器带宽,StratixV还包括一个7×72位1,600MbpsDDR3存储器接口,以及所有I/O上的1.6GbpsLVDS通道。

除了高带宽特性,StratixV对内核体系结构也进行了改进,提高了面积和逻辑效率以及系统性能,包括增加了新的自适应逻辑模块(ALM)体系结构,即在最大的器件中额外增加了800K寄存器以提高逻辑效率,这一体系结构适用于需要大量流水线和寄存器的设计。

新器件还具有M20K模块的增强嵌入式存储器结构以提高面积效率和性能。

特别值得注意的是,新器件内置业界首款精度可调的DSP模块,实现了效率最高、性能最好的多精度DSP数据通路。

此外,新器件提供的部分重新配置功能可以使设计人员重新配置部分FPGA,而其他部分仍然正常运行。

硬核IP的集成是另一重点,StratixV是Altera目前硬核IP集成度最高的器件,其增强功能包括PCIeGen3,Gen2,Gen1、40G/100G以太网、CPRI/OBSAI、Interlaken、SerialRapidIO(SRIO)2.0和万兆以太网(GbE)10GBASE-R。

增强了读/写通路的存储器接口包括DDR3、RLDRAMII和QDRII+。

罗嘉鸾进一步表示,Altera在28nmFPGA的创新技术还在于嵌入了HardCopy模块。

这一独特的方法使Altera能够迅速改变FPGA中的增强功能,在3到6个月内完成专用器件型号的开发。

嵌入式HardCopy模块为用户提供了700K等价LE,与软核逻辑实现相比,功耗降低了65%。

此次针对StratixV用户,Altera将提供HardCopyVASIC器件,详细信息也即将披露。

预计,StratixV样片将于2011年第一季度开始发售,而2010年第二季度会推出开发工具QuartusII10.0。

利用FPGA和CPLD数字逻辑实现ADC

技术分类:

可编程器件 |2010-06-01

中电网

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。

除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

与数字逻辑相连接时,ADC是一种常用的模拟功能块,例如,FPGA或CPLD连接至模拟传感器的现实世界时,ADC是不可或缺的。

本文将阐述采用莱迪思半导体公司的参考设计和演示板来实现低频率(DC至1KHz)和高频率(高达50KHz)ADC。

针对每种设计的应用示例,即网络交换机中的系统.和语音通信系统中的频率检测将在文中验证。

模数转换器的实现

一个简单的模数转换器可以通过添加一个简单的RC电路至FPGA或CPLD的LVDS输入来实现。

正如图1的左下角所示,RC网络在LVDS输入的一端,模拟输入则在另一端。

LVDS输入将作为一个简单的模拟比较器,如果模拟输入电压高于RC网络的电压,将输出数字“1”。

通过改变RC电路的输入电压(来自FPGA/CPLD的通用输出),LVDS比较器可用于分析模拟输入电压,以创建一个准确的数字表示。

模拟至数字控制模块可以用多种方式实现,取决于模拟输入的频率、所需的分辨率和可用的逻辑资源。

用简单的逐次逼近寄存器可以处理低频信号,如图1左上角的选项1。

实现较高频率的情况如图1右上角所示,可以用Δ-Σ调制器功能来实现,它由采样寄存器和级连梳状(CIC)滤波器组成。

一旦构建了数字信号,就可以对数字输出进行可选的过滤,以去除任何由于系统噪音或反馈抖动所引入的不必要的高频分量。

在可选数字滤波模块后面,可选的存储器缓冲区可用于调试/测试目的。

通过存储缓冲器对数字输出采样,然后通过JTAG端口扫描输出,到达运行信号分析软件的个人计算机。

图1:

模数转换器基本框图:

低频和高频情况。

低频/最小逻辑ADC实现

在低频/最小逻辑实现情况中,采样控制模块控制逐次逼近寄存器,相关的输出信号随时加到RC电路。

因此RC电路的电压上升或下降,以响应相关的输出状态,输出状态是变化的。

LVDS输入比较模拟输入与RC电路电压的变化。

因此,RC电路的电压是用来“发现”模拟输入电压。

图2的例子中,静态模拟输入(由橙色虚线来表示)设置为不到整个输入电压范围的一半。

垂直的黑色虚线表示SAR采样点之间的时钟数目,用绿色虚线来表示。

第一次测量需要8个时钟,下一次需要4个时钟,等等类似。

最初,通过在相关输出上加逻辑“1”,RC电路被设置为模拟输入的整个电压摆幅的一半。

一旦电压达到这个点的一半,LVDS输入的输出将指示模拟输入值是否高于或低于RC电路电压。

如果模拟电压较高,数字输出的最高有效位是逻辑“1”。

如果模拟电压较低,则数字输出为逻辑“0”。

SAR移到下一位,采样时间减半(为整个电压摆幅的四分之一)。

这个过程不断重复,直到A/D转换器达到所需的精度。

在图2中的例子中,观察RC电路电压是如何逐渐接近模拟输入值。

在这个简单例子中,SAR(0101)的4位数字输出展示在图的底部。

图2:

基于SAR的A/D转换器运作实例。

低频设计可以用来监测几个模拟电压的电平,这些电平表示各种电源电压和环境传感器的输出。

CPLD实现可以监控PCB的电源电压(3.3V,2.5V和1.8V),以及温度和湿度传感器和开放式机箱的报警。

为测量多个模拟输入,可针对每个模拟电压连同附加的RC电路采用一个LVDS输入。

由于模拟电压是缓慢改变的,LVDS输出可多路复用,这样在每个输入之间就可以共享数字逻辑功能。

低频/最小逻辑ADC的测试结果

无需可选数字滤波电路的低频/最小逻辑电路已经用一块*估板在莱迪思的MachXOCPLD上实现,并使用电压范围为0V至3.3V的0.8Hz输入信号。

如图1所示,采用可选的存储器缓冲区及莱迪思ispLEVER设计软件的RevealLogicAnalyzer功能。

该功能将缓冲存储器添加至目标设计,并加入控制数字信号采集、数据缓冲和通过JTAG电缆输出数据到计算机所需的逻辑。

在测试过程中,使用Linear公司的PScope软件在捕获的数据上运行FFT。

该电路对0.8Hz模拟输入的响应显示在图3的上半部分。

图3:

A/D转换器的结果实例:

低频和高频选项。

接收到的数字信号显示在PScope屏的顶部窗口中。

纵轴用来测量代码步长(0到255),横轴用来测量采样(在这个例子中有1024个样本)。

在边栏的右上角报告频率,如f1(基本)频率。

FFT的结果显示在窗口的下面,根据它们的dB水平通过纵轴显示谐波频率。

从FFT产生的关键参数显示在右下侧栏,其中包括有效位数(ENOB)和信噪比(SNR)。

这些结果表明,输入信号已成功转换为具有好的分辨率和信噪比的数字信号。

基于CPLD/FPGA的多功能分频器的设计与实现

技术分类:

可编程器件 |2009-11-23

武汉理工大学吴玉昌胡荣强王文娟

引言

分频器在CPLD/FPGA设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源,但是对于要求奇数倍分频(如3、5等)、小数倍(如2.5、3.5等)分频、占空比50%的应用场合却往往不能满足要求。

硬件工程师希望有一种灵活的设计方法,根据需要,在实验室就能设计分频器并马上投入使用,更改频率时无需改动原器件或电路板,只需重新编程,在数分钟内即可完成。

为此本文基于CPLD/FPGA用原理图和VHDL语言混合设计实现了一多功能通用分频器。

分频原理

偶数倍(2N)分频

使用一模N计数器模块即可实现,即每当模N计数器上升沿从0开始计数至N时,输出时钟进行翻转,同时给计数器一复位信号使之从0开始

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《JAVA编程基础》课程标准软件16级.docx

《JAVA编程基础》课程标准软件16级.docx