微机原理与接口技术试题与答案.docx

微机原理与接口技术试题与答案.docx

- 文档编号:10504962

- 上传时间:2023-02-17

- 格式:DOCX

- 页数:37

- 大小:37.08KB

微机原理与接口技术试题与答案.docx

《微机原理与接口技术试题与答案.docx》由会员分享,可在线阅读,更多相关《微机原理与接口技术试题与答案.docx(37页珍藏版)》请在冰豆网上搜索。

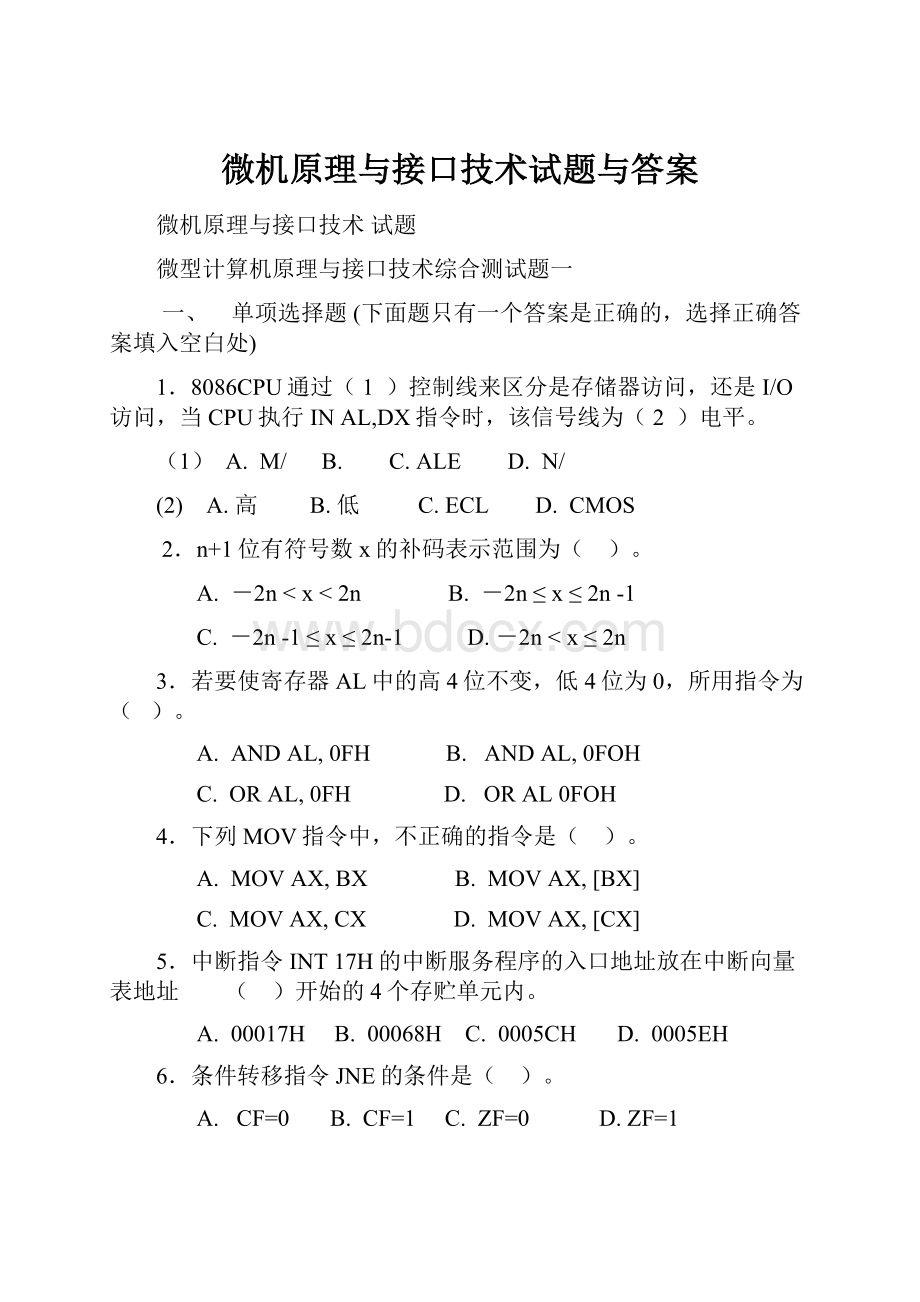

微机原理与接口技术试题与答案

微机原理与接口技术试题

微型计算机原理与接口技术综合测试题一

一、 单项选择题(下面题只有一个答案是正确的,选择正确答案填入空白处)

1.8086CPU通过(1 )控制线来区分是存储器访问,还是I/O访问,当CPU执行INAL,DX指令时,该信号线为(2 )电平。

(1) A. M/ B. C.ALE D. N/

(2) A.高 B.低 C.ECL D. CMOS

2.n+1位有符号数x的补码表示范围为( )。

A. -2n C. -2n-1≤x≤2n-1 D.-2n 3.若要使寄存器AL中的高4位不变,低4位为0,所用指令为( )。 A. ANDAL,0FH B. ANDAL,0FOH C. ORAL,0FH D. ORAL0FOH 4.下列MOV指令中,不正确的指令是( )。 A. MOVAX,BX B. MOVAX,[BX] C. MOVAX,CX D. MOVAX,[CX] 5.中断指令INT17H的中断服务程序的入口地址放在中断向量表地址 ( )开始的4个存贮单元内。 A. 00017H B. 00068H C. 0005CH D. 0005EH 6.条件转移指令JNE的条件是( )。 A. CF=0 B. CF=1 C. ZF=0 D.ZF=1 7.在8086/8088CPU中,一个最基本的总线读写周期由 (1)时钟周期(T状态)组成,在T1状态,CPU往总线上发 (2)信息。 ⑴ A. 1个 B. 2个 C. 4个 D. 6个 ⑵ A. 数据 B.地址 C.状态 D. 其它 8.8086有两种工作模式,最小模式的特点是 (1),最大模式的特点是 (2)。 ⑴ A.CPU提供全部控制信号 B.由编程进行模式设定 C.不需要8286收发器 D.需要总线控制器8288 ⑵ A.M/ 引脚可直接引用 B.由编程进行模式设定 C.需要总线控制器8288 D.适用于单一处理机系统 9.在8086微机系统的RAM存储单元器0000H: 002CH开始依次存放23H,0FFH,00H,和0F0H四个字节,该向量对应的中断号是( )。 A. 0AH B. 0BH C. 0CH D. 0DH 10.真值超出机器数表示范围称为溢出,,此时标志寄存器中的( )位被置位 A. OF B AF C PF D CF 11.8086系统中内存储器地址空间为1M,而在进行I/O读写是,有效的地址线是( ) A.高16位 B. 低16位 C.高8位 D. 低8位 12.8086 CPU中段寄存器用来存放( ) A. 存储器的物理地址 B.存储器的逻辑地址 C.存储器的段基值 D.存储器的起始地址 13.8259A可编程中断控制器的中断服务寄存器ISR用于( ) A.记忆正在处理中的中断 B.存放从外设来的中断请求信号 C.允许向CPU发中断请求 D.禁止向CPU发中断请求 14.8253可编程定时/计数器的计数范围是( ) A. 0-255 B. 1-256 C.0-65535 D.1-65536 15.在8086中,(BX)=8282H,且题中指令已在队列中,则执行INC[BX]指令需要的总线周期数为() A.0 B.1 C.2 D.3 16.8086中,( )组寄存器都可以用来实现对存储器的寻址。 A.AX,SI,DI,BX B.BP,BX,CX,DX C.SI,DI,BP,BXD.BX,CX,SI,DI 17.微机系统中若用4片8259A构成主、从两级中断控制逻辑,接至CPU的可屏蔽中断请求线INTR上,最多可扩展为( )级外部硬中断。 A.32 B.29 C.28 D.24 18.在8086宏汇编过程中不会产生指令码,只用来指示汇编程序如何汇编的指令是 ( ) A.汇编指令 B.伪指令 C.机器指令 D.宏指令 19.连接到64000h-6FFFFh地址范围上的存储器是用8k×8 RAM芯片构成的,该芯片要( )片。 A.8片 B.6片 C.10片 D.12片 20.8086/8088指令OUT 80H,AL表示 ( ) A. 将80H送给AL B.将80H端口的内容送给AL C.将AL的内容送给80H端口 D.将AL内容送给80H内存单元 二.改错(若有错,请指出错误并说明原因) 1.堆栈操作应满足先进先出原则。 ( ) 2.CPU在未执行完当前指令的情况下,就可响应可屏蔽中断请求。 ( ) 3.8086CPU标志寄存器共有16位,每一位都有含义。 ( ) 4.条件转移指令只能用于段内直接短转移。 ( ) 5.控制器的基本功能是: 由程序计数器PC控制程序的有序运行,并完成各种算术逻辑运算。 ( ) 6.在8259A级连系统中,作为主片的8259A的某些IR引脚连接从片,同时也可以在另一些IR引脚上直接连接外设的中断请求信号端。 ( ) 7.8086的中断分为可屏蔽中断和不可屏蔽中断两种。 ( ) 8.串行接口中“串行”的含意仅指接口与外设之间的数据交换是串行的,而接口与CPU之间的数据交换仍是并行的。 9.字长一定的情况下,原码、反码和补码所能表示的二进制真值范围是相同的。 ( ) 10.所有进位计数制,其整数部分最低位的位权都是1( ) 三、填空题 1.某存贮器单元的实际地址为2BC60H,该单元在段地址为2AFOH中的偏移地址是__________。 2.8086CPU复位后,寄存器中的值将进入初始态,问(CS)=__________, (IP)=__________,(DS)=__________。 3. 8086/8088CPU内部结构按功能分为两部分,即_________ 和__________。 4.CPU对外设进行数据传送的方式有几种,即__________,___________,或___________。 5. CPU从主存取一条指令并执行该指令的时间称为__________,它通常用若干个__________ 来表示,而后者又包含有若干个__________ 。 6. 8086/8088CPU提供了接受外部中断请求信号的引脚是__________ 和 __________。 7.-128的补码是 8.填入适当指令,使下面程序实现用移位、传送、加法指令完成(AX)与10相乘运算: SHL AX,__________ MOV DX,AX MOV CL,__________ SHL AX,CL ADD__________ 9.时序控制方式有同步方式和 10.大部分DMAC都拥有单字节传送, 传送,和成组传送方式 四.阅读程序并回答问题 1、 已知: (AX)=2233H,(BX)=5566H,执行了下面的程序段后,(AX)=_______,(BX)=______. CMPAX,BX JG NEXT XCHGAX,BX NEXT: NEGAX 2、 已知: (AX)=6666H,(BX)=0FF00H,(CF)=0。 在执行下面程序段后: (AX)=____,(BX)=____,(CF)=____. MOVAX,5555H ANDAX,BX XORAX,AX NOTBX 五、综合应用 1.8255A接口电路如图所示。 已知8255A控制字寄存器的端口地址为103H,编写8255A初始化程序和循环彩灯控制程序。 初始时D0亮,其余不亮,D0亮一秒后移位一次,D1亮,其余不亮,以此类推每隔一秒移位一次,每移位8次为一个循环.共循环8次。 要求用汇编语言写出满足上述要求的程序段(已知一个延时1秒的子程序入口地址为DELAY1S)。 2.已知存储器地址空间分配、RAM芯片(4K×4)、如图所示,请完成如下任务: (1)图所示RAM芯片有几根地址线? 几根数据线? 用该RAM芯片构成图中所示存储器地址空间分配,共需要几个芯片? 共分几个芯片组? (2)设CPU的地址总线为20位,数据总线8位,画出这些芯片按图所示的地址空间构成的RAM存储器极其与CPU间的连接图(包括3-8译码器构成的片选8译码电路)。 ┏━━━━┓ ┏━━┷━━━┓ ┏━━━━━━┓ 0000H┃ RAM1 ┃ ┃ ! CS ┃ ─┨G1 Y0! ┠─ ┃ ┃ →┃A11 ┃ ─┨! G2a Y1! ┠─ 2000H ┠────┨ .┃ ┃ ─┨! G2b ┃ ┃ 空 ┃ .┃RAM(4K×4)┃ ┃ .┃ ┃ ┃ .┃ ┃ ┃ .┃ 6000H ┠────┨ →┃A0 ┃ ┃ .┃ ┃ RAM2 ┃ ┃ ┃ ┃ ┃ ┃ ┃ →┃! WE ┃ ─┨C ┃ 7000H ┠────┨ ┃ ┃ ─┨B ┃ ┃ 空 ┃ ┃ ┃ ─┨A Y7! ┠─ ┃ ┃ ┃ D3-D0 ┃ ┃ ┃ ┗━━━━┛ ┗━━━━━━┛ ┗━━━━━━┛ ↓ RAM芯片 微型计算机原理与接口技术综合测试题二 一、单选题 ( )1.8086CPU在执行MOV AL,[BX]指令的总线周期内,若BX存放的内容为1011H,则和A0的状态是 。 A.0,0 B.0,1 C.1,0 D.1,1 ( )2.设x=-46,y=117,则[x-y]补和[x+y]补分别等于 。 A.D2H和75H B.5DH和47HC.2EH和7lH D.47H和71H ( )3.8086CPU在进行无符号数比较时,应根据 标志位来判别。 A.CF和OF B.CF和PF C.CF和ZF D.ZF和OF ( )4.执行下列程序后,(AL)= 。 MOV AL,92H SUB AL,7lH DAS A.21 B.11 C.21H D.11H ( )5.下列指令中正确的是 。 A.MOV AX[SI][DI] B.MOV BYTEPTR[BX],1000 C.PB8 EQU DS: [BP+8] D.MOV BX,OFFSET[SI] ( )6.在PC/XT中,NMI中断的中断矢量在中断矢量表中的位置 。 A.是由程序指定的 B.是由DOS自动分配的 C.固定在08H开始的4个字节中 D.固定在中断矢量表的表首 ( )7.在8086中,(BX)=8282H,且题中指令已在队列中,则执行INC[BX]指令需要的总线周期数为 。 A.0 B.1 C.2 D.3 ( )8.微机系统中若用4片8259A构成主、从两级中断控制逻辑,接至CPU的可屏蔽中断请求线INTR上,最多可扩展为 级外部硬中断。 A.32 B.29 C.28 D.24 ( )9.当存储器读写速度较慢时,需产生一个READY信号以实现与CPU的同步,CPU将在总线周期的 时候采样该信号。 A.T2下降沿 B.T3下降沿 C.T2上升沿 D.T3上升沿 ( )10.8086中, 组寄存器都可以用来实现对存储器的寻址。 A.AX,SI,DI,BX B.BP,BX,CX,DX C.SI,DI,BP,BX D.BX,CX,SI,DI 三、填空题 1. 已知(AL)=0101110lB,执行指令NEGAL后再执行CBW,(AX)= 。 2. 在动态存储器2164的再生周期中,只需要 地址,所以在和这两个信号中,只有 变为低电平。 3.过程可重入是指 ,用 传递参数过程才可实现重入。 4. 若(AL)=01001001B,执行ADD AL,AL指令后,再执行DAA命令,则(AL)= ,(CF)= ,(AF)= 。 5. 已知指令序列为: MOV AX,0FFBDH MOV BX,12F8H IDIV BL 此指令序列执行后,(AX)= ,(BX)= 。 6. 微型计算机中,CPU重复进行的基本操作是: 、 和 。 7. 若(CS)=4200H时,物理转移地址为4A230H,当CS的内容被设定为7900H时,物理转移地址为 。 8. 8259A工作在8086模式,中断向量字节ICW2=70H,若在IR3处有一中断请求信号,这时它的中断向量号为 ,该中断的服务程序入口地址保存在内存地址为 H至 H的 个单元中。 四、程序阅读 1.阅读下列程序,写出程序执行后数据段BUF开始的10个内存单元中的内容。 DATASEGMENT BUF DB08H,12H,34H,56H,78H,9AH,0BCH,0DEH,0F0H,0FFH KEY DB78H DATAENDS CODESEGMENT ASSUME CS: CODE,DS: DATA,ES: DATA START: MOVAX,DATA MOVDS,AX MOVES,AX CLD LEA DI,BUF MOVCL,[DI] XORCH,CH INC DI MOV AL,KEY REPNE SCASB JNE DONE DECBUF MOVSI,DI DECDI REP MOVSB DONE: MOVAH,4CH INT 21H CODE ENDS ENDSTART 执行结果: BUFDB 、 、 、 、 、 、 、 、 、 2.在内存的NUM单元中有一个字节的带符号二进制数(补码表示),下列程序是将其对应的十进制数输出到显示器上。 请对程序中的三处错误进行修正,并在空白处填上适当的语句。 DATA SEGMENT NUM DB ? BUFFER DB 10DUP(? ) DATA ENDS STACK SEGMENT PARA STACK‘STACK’ DB 100HDUP(? ) STACKEVDS CODE SEGMENT ① START: MOVAX,DATA MOVES,AX MOVDS,DATA MOVCL,NUM LEA DL,BUFFER ② MOVAL,0DH STOSB MOVAL,0AH STOSB MOVAL,CL OR AL,AL JS PLUS ③ MOVAL,‘-’ JMP GOON PLUS: MOVAL,‘+’ GOON: STOSB MOVBL,64H CALL CHANGE MOVBL,0AH CALL CHANGE MOVAL,30H ADDAL,CL STOSB MOVAL,‘$’ STOSB LEA DX,BUFPER MOVAH,9 INC 21H ;输出十进制 MOVAH,4CH INT 21H CHANGE PROC NEAR MOVDL,0 AGAIN: SUB CL,BL JC DOWN INC DL JMP AGAIN DOWN: ④ MOVAL,30H ADDAL,DL STOSB ⑤ CHANGE ENDP CODE END ENDSTART 五、存储系统分析与设计 已知RAM芯片和地址译码器的引脚如题五图所示,试回答如下问题: (1)若要求构成一个8K×8的RAM阵列,需几片这样的芯片? 设RAM阵列组占用起始地址为El000H的连续地址空间,试写出每块RAM芯片的地址空间。 (2)若采用全地址译码方式译码,试画出存储器系统电路连接图; (3)试编程: 将55H写满每个芯片,而后再逐个单元读出做比较,若有错则CL=FFH,正确则CL=77H。 D4~D1 微型计算机原理与接口技术综合测试题三 一、单选题 ( )1.在8086宏汇编过程中不会产生指令码,只用来指示汇编程序如何汇编的指令是 。 A.汇编指令 B.伪指令 C.机器指令 D.宏指令 ( )2.在CMPAX,DX指令执行后,当标志位SF、OF、ZF满足下列逻辑关系(SF⊕OF)+ZF=0时,表明 。 A.(AX)>(DX) B.(AX)≥(DX) C.(AX)<(DX) D.(AX)≤(DX) ( )3.8086微机系统的RAM存储单元中,从0000H: 002CH开始依次存放23H,0FFH,00H,和0F0H四个字节,该向量对应的中断号是 。 A.0AH B.0BH C.0CH D.0DH ( )4.8255的A口工作在方式1输入时,其中断允许控制位INTE的开/关是通过对 的按位置位/复位操作完成的。 A.PC0 B.PC2 C.PC4 D.PC6 ( )5. 在进入DMA工作方

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 微机 原理 接口 技术 试题 答案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx