两级开环比较器的设计.docx

两级开环比较器的设计.docx

- 文档编号:10490819

- 上传时间:2023-02-13

- 格式:DOCX

- 页数:34

- 大小:656.21KB

两级开环比较器的设计.docx

《两级开环比较器的设计.docx》由会员分享,可在线阅读,更多相关《两级开环比较器的设计.docx(34页珍藏版)》请在冰豆网上搜索。

两级开环比较器的设计

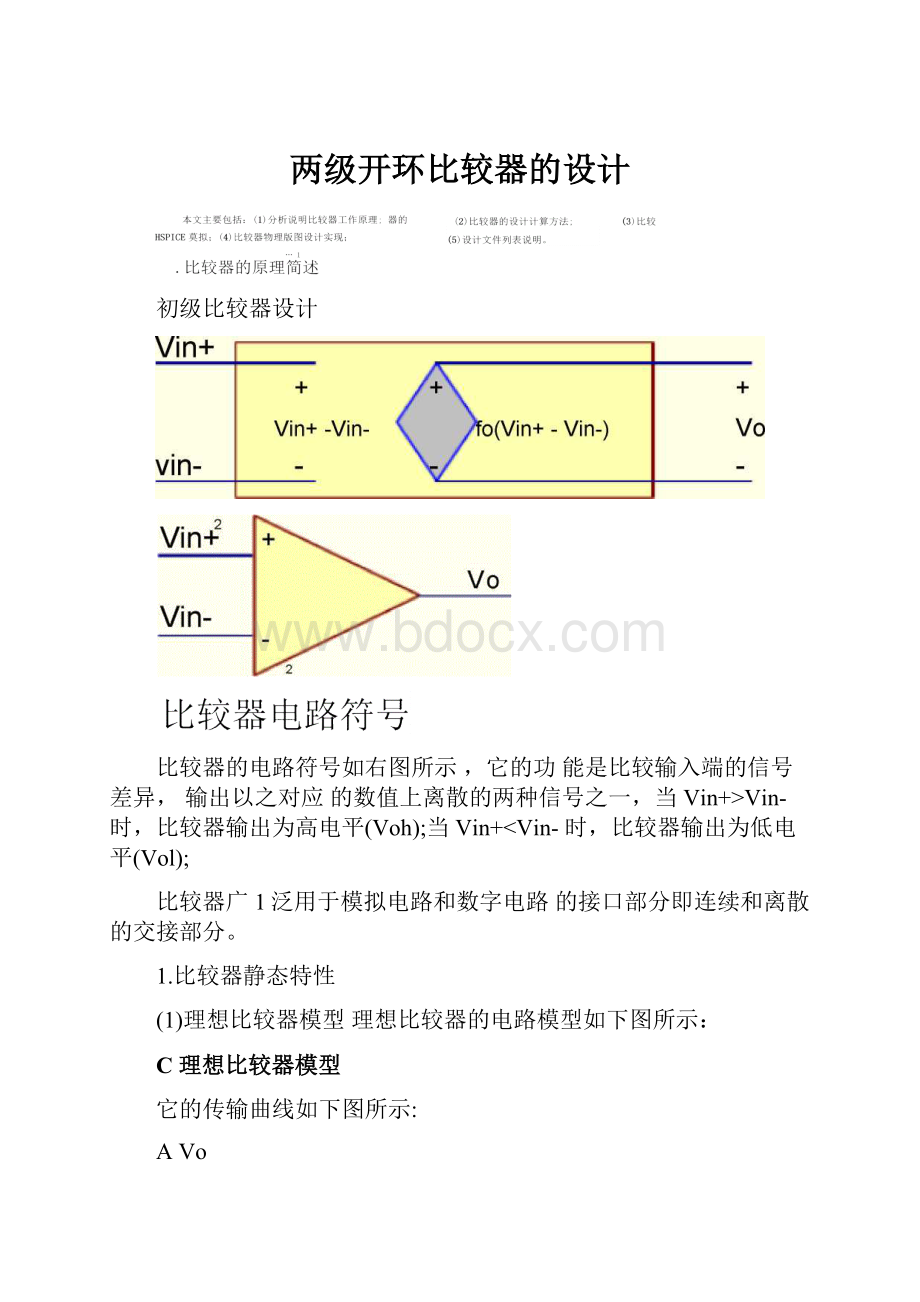

初级比较器设计

比较器的电路符号如右图所示,它的功能是比较输入端的信号差异,输出以之对应的数值上离散的两种信号之一,当Vin+>Vin-时,比较器输出为高电平(Voh);当Vin+ 比较器广1泛用于模拟电路和数字电路的接口部分即连续和离散的交接部分。 1.比较器静态特性 (1)理想比较器模型理想比较器的电路模型如下图所示: C理想比较器模型 它的传输曲线如下图所示: AVo Voh Vin+-Vin- 传输曲线可以用数学函数表示如下: f八,V)Voh,when(VnVn)0To(VinVin)TT;—: TTVol,when(VnVn)0 AVohVol VihVil (2)有限增益比较器模型 有限增益比较器的电路模型如下图所示: 有限增益比较器模型 它的传输曲线如下图所示: 传输曲线可以用数学函数表示如下: fl(VinVin)1 rVoh,when(VinVin)Vih ]A(VinVin),whenVilM%)V, 1 Vol,,when(VinVin)V^ AVohVo1,为一个有限值 VihVil (3)包含输入失调电压的比较器 包含输入失调电压比较器电路模型如下图所示: 包含输入失调电压比较器模型 它的传输曲线如下图所示: 包含输入失调电压比较器的传输曲线 其中的Vos为输入失调电压,它被定义为: 实际比较器输出电压为零时,输入端所加的电压,它是比较器的一个重要参数,跟比较器的精度有密切的关系,而且它的温漂很难补偿。 (4)比较器其他的静态特性 共模输入电压范围,还有和过度区特性相 差分输入电阻和电容,输出电阻,共模输入电阻, 关联的噪声。 这些和运放很相似,可以同样建模。 2.单极点简单比较器动态特性 定义比较器的时延为: 比较器的输入激 比较器动态特性中的重要特性之一为传输时延, 励和输出转换之间的时延,如下图所示: (1)小信号时延 假设比较器的最小输入电压差为比较器的精度,定义比较器的最小输入电压为: A(s)Av(0)Av(0)代(s)———-s1sc1 Wc 那么,我们下面就可以分析比较器的时延: 根据时延的定义和Av(S),进行拉普拉斯逆变换,得到输入为阶跃信号Vinmin的时域响应如 下式: VohVolA/c\r/itp/C-,.zc\r/itp/cVohVol F代㈣1e]VinminAv(0)[1e]冇 tPmaxcln (2)0.693c 同理可以得到更为普遍的结果: 当输入激励信号为阶跃信号kVjnmin,相应得输出响应时延为: 2k tpcin(二,显然在线性响应的情况下,增大k可以有效的减小时延tp。 对应的关 2k1 系可以表示如下图: (2)大信号时延 大信号情况下,时的传输时延为: VohVo1,出现摆率限制时, 2SRTitle dV1dQ丄charge/discharge dtCdt Size B Date: File: Number Revision 29-Jun-2006 C: \DocumentsandSettings\yoyo桌面\TEMPDWQQ\sByoc_course_desgin_homework\soc_cou Sheetof 三.比较器的设计 以下侧重分析时延的限制因素和设 比较器的传输时延始终是我们关注的一个重点指标,计时常常引用的公式。 1.两级开环比较器的线性响应设计 NMOS输入管两极开环比较器的电路拓扑结构如下图所示: Vdd [VbiaS Vss NMC输入两级比较器 6(VDDVG6MIN 显然, (2)两级比较器的特性 A部分 .第一级简单CMOSOTA特性 COMSOTA的小信号等效电路如下图所示: 由以上的电路原理图可以得到第一级简单 gm1*Vgs1 gm2*Vgs2+gm4*Vgs4 第一级: 简单COMSOTA信号等效电路 其中: 1 rn4rds1//rds3//gm3 Vout(gm1Vgs1gm4gm1Vgs1rn4)rn5gm1Vgs1(1gm4rn4)rn5 由以下B部分的分析可以知道: 第一级简单CMOSOTA可以等效成一个对差模信号跨导为 Gm的放大管,而其中的电容对总的极点没有影响,如下图所示: 第一级进一步等效电路 Vid为输入差模信号。 由于输入信号的内阻一般很小,所以输入节 iNumber 3为共模信号相关而与差模信号无 4的时间常数很小也不可能形成主极点;最有可能形成 即第一级的节点电容对整体电路的特性没有决定s乍用,Settin利利s\wangq桌面\TEM Title B部分 第一、二级联合整体电路特性 根据NMOS输入两级比较器电路图可知: Size点1和节点2的时间常数很小不可能形成主极点;节点 A4关;M3二极管连接方式决定了节点, 主极点的地方为节点5和节点6, 用A部分的分析结果可以得到整体电路的小信号等效电路如下图所示: 两级开环比较器小信号等效电路 5节点对地电阻rds24rds2//rds4,5节点对地电容Cn5, Title Size Number Revision 6节点对地电阻rds67rds6//rds7 6节点对地电容Cn6, 6节点和5节点间的电容 根据基尔霍夫电压环路(组并解得: Cc针对比较器电路,采用开环模式,通常使Cc最小化,以得到最 大的带宽和较快的响应)。 KVL)和电流节点(KCL定理,可以得到该小信号等效电路的方程 为了计算的方便,Av(s)可以采用节点时间常数近似方法估算,它的另一种表示方式如 下: Av(0)代(s)ss(—1)(—1) P1P2 Vo(s)=Av(s)Vin(s),对它进行拉普拉斯逆变换可以得到时域的响应为: 再进一步简化得: 2 Vo(tn)mk/ 令Vo(tn)(VohVol)/2,解得: tpn JmA(0)Vn VohVol Vinmin mVn 1 Vmk tPtpn1m Vmk %#・ P2,k),这就是估算线性线性响应传输时延的关系式。 p1Vinmin 附带说明一下如何选择摆率受限或线性响应受限来估算比较器的传输时延: 为了比较线性响应受限和摆率受限,我们对Vo(t)Av(0)[1 t/1 P2e P1 p2 t/2 P^]Vin(t) P1P2 进行归1化处理得: Vo(tn)A^w^c1-^re^ m1 —emtn,其中: m匹1,tn m1P1 tp1 对上式进行两次求导并令其等于 0可以得到归一化响应的最大斜率为: dVo(tn) dtn Inm 冇e maxm1 Inm m m1] () 而两级开环比较器的输出摆率为: SR C2 () SR I6I7 C2 6(VddVg6MINVtp C2 2 I7) 比较 ()、和(), 当VinVinmin且摆率比()小时,则应采用摆率来估算比较器电路的时延。 需要特别强调的是: 如果是线性响应受限则极点的位置十分重要,的充放电的能力变得更为重要。 (4)设计常用公式: 为设计方便,现将常用的设计公式及步骤总结如下: IP2|C2 如果是摆率受限则对电容 ①p1 p2 tpVmk"7 I6 216W7 K'p(VSD6SAT)L7 2I7 ~—~夢,VSD6SATVddVoh,VDS7SATVolVss KN(VDS7SAT) ③假设一个C1的值’计算I5I72C ④WW L3L4 2,VSG3VddVicm ⑤gm1 Av(0)(gds2gds4)(gds6gds7) gm6 2Kp'WJ6 gm6 L6 VohVol Vinmin g2 畀A(0) KNI5 Cbd2 Cbd4、 ad2 W2(L1 L2 L3) PD2 2(W2 L1 L2 L3) ad4 W4(L1 L2 L3) PD4 2(W4 L1 L2 L3) 计算出 C1,如果计算出的 C 骤,直道计算出来的C1小于假设的 Cgd2 Cgs6 大于在第三步中假设的C1,则必须加大C1且重复3~6的步 C1为止。 —W5 ⑦VdS5SATVicmVgs1Vss, L5 如果Vds5sat小于100mV则增大一- L1 2.两级开环比较器的摆率响应设计 (1)设计中用到的分析方法 设计中的分析法方法法和“1”并利用根据基尔霍夫电压环路( (2)时延的估算 在大多数的情况下,两级开环比较器会被驱动到摆率受限,此时,传输时延由下式计算: 部分讲解的类同,KVL)和电流节点( 重点要理解电路的小信号等效电路,KCL定理来求解,并进行设计计算。 iiCidv Ci v^,其中: Ci为第i级的对地电容,由该式可以得到第i级的传输时 ti 延为: titi Ci 上,总的传输时延为tpCi—百。 IiiIi (2)设计常用公式 为设计方便,现将常用的设计公式及步骤总结如下: ①I7 I6 -dvout C2dt C2(VohVol) tp217 厶.2,VsD6SATVddVoh,VdS7SATVolVss K'p(VsD6SAT)L7K'n(Vds7sat) 216 ③假设一个C1值并在以后检查 ④I5 c単 dt Ci(VohVol) tp I5 2,VSG3VddVicmVTN ⑥gm1 Av(0)(gds2gds4)(gds6gds7) gm6 gm6 L6 ad2 W2(L1 L2 L3) PD2 2(W2 L1 L2 L3) ad4 W4(L1 L2 L3) PD4 2(W4 L1 L2 L3) 计算出 C1,如果计算出的 C g2 VohVol Vinmin 畀A(0) KN! 5 Cbd2Cbd4 大于在第三步中假设的C1,则必须加大C1且重复3~6的步 C1为止。 骤,直道计算出来的C1小于假设的 3.复合比较器(前置线性放大级2+锁存再生级)设计 在参考材料中的复合比较器的电路拓扑结构如下图所示: 为了设计计算电路的参数,必须首先要分析电路的特性,以下部分析该电路的主要特性: 上图复合比较器是钟控动态比较器,电路结构上由两级组成: 前级是前置线性放大器,后级mber A4 Date: 30-Jun-2006 File: C: \DocumentsandSettings\wangq桌面\TEM 是再生锁存器。 前置线性放大器由MB、M1、M2、M3和M4构成,再生锁存器M7、M8、 M9和M10构成,而其他的M5、M6和M11是动态时钟控制开关管。 为了保证最小的传输时延,它的设计思想在于: 强调前级的大带宽和后级的高摆率,前级按负指数响应把输入信 号放大到一定的值Vx,接着锁存器按照正指数响应把这信号Vx进一步放大,这样可以使整体的传输延迟tpt1t2最小化。 可以用如图阶跃响应所示: (1)所存器级传输时延的设计计算锁存器级的核心电路结构如下图所示: 锁存再生级 它的小信号等效电路如下图所示: 2omm vo2 ro=! 4 o 1 ―! =! 1 vo1/ \r +R1十 L/i\ ]R2十 gvo1'//'^ ~j C2+ 锁存再生级小信号等效电路 vo2 R1: 节点 R2: 节点 C1: 节点 C2: 节点 1对地电阻;2对地电阻; 1对地电容;2对地电容; Vo17s: 是vo1的t初值,且为阶跃信号; Vo27s: 是vo2的初值,且为阶跃信号;由小信号等效电路可以得到节点方程组如下: SizeNumber r(gm7 4gm8 3 gm9)Vo2a4G1Vo1 Date: gm10)VoFileG2Vo2 点Um程er Vo1 Revision Vol Vo2 其中: 假设 sG(Vo1) s 30-Jun-2006V(sC2(Vo2ds '(gm7gmJRVSRC11』CJVo2'SR2C211RCi,2 (gm7gm9)Vo2GVo1sC1V)1C1Vo1'0 Sheetof (gm8g^o)桌面TGDP_2WQQC2V_CouCeVoesgin0homework\protel_doc\so 4 刊' (gm7gm9)Ry s11o2 (gm8gm10)R2V SR2C21 Vo2 (gm8gm10)R2 Vol R2C2 MOS管采用对称设计使他们的跨导相等,令: gm gm7 gm9gm8gm10, RR|R2,CC1C2, VoVo2 Vol, Vi Vo2' Vol',则可以解得: Vi Vos(12gmR) Vi 12gmR s12gmR 求上式的拉普拉斯逆变换的时域响应为: vo(t)Vi'e Viet(12gmR)/ 其中: /、I• s'112gmR e2gmRt/ Vi et/L Vi,即: vo(t)et/LVi 其中. /、I•L 0.67WLCox2gmR2j2k'(W/L)l0.34厝 要求锁存器级的传输时延,可以令: Vo(t)et/ Vi (VohVol)/2,解得传输时延为: tpLln( VohVo1),显然要改善传输时延应该从 2Vi 足够大的Vi可以使传输时延明显地减小。 (2)前置线性放大级传输时延的设计计算 前置线性放大级核心电路结构如下图所示: ^Vbiax M1 PMOS4 M3 NMOS4 V两方面着手解决。 特别是选择 MB PMOS4 「M2 M4 护4 pM; NMOS4 Mt M8 NMOS4 Vss 前置线性放大级 为分析前置级电路,先假设M7和M8管不起作用,则这电路变成了简单CMOSOTA电路, 它的性能在前面已经分析过了,不过要注意这里的M3和M4管应该是处于线性区而不是 饱和区,因为时钟信号点位接近Vdd,具体结果可以参考前面的分析;但是,M7和M8实 际上是可能流过电流,那么这个电路就变得复杂,有待于进一步的分析,不过分析的主体思想为: 考察MOS晶体管的工作状态;画出电路的小信号等效电路;由基尔霍夫定理电路方程组求解。 四.实际设计比较器HSPICE模拟 SizeNumber A4 Date: 30-Jun-2006 File: Revision Sheetof 桌MTEMP_WnQQ\soc_course_desgin_homework 4 以上设计计算的电路参数,只是个估算值,一般都要调整,这时我们可以利用 来模拟,一方面,可以检验电路的功能是否正确,另一方面,由模拟的结果反过来调整电路 的参数。 直到得到满意的性能指标为止。 HSPICE 实际采用的两级开环比较器的电路原理图及相关说明(附带文件: 4 vdd PM1 "pmos4",W/L=25/2.5 vdd PM2 "pmos",W/L=25/2.5 vdd PM3 "pmos",W/L=25/2.5 vdd PM4 "pmos",W/L=12.5/2.5 □nr> ]lblas》 vdd》 &,W/L=12.5/2.5 ' VSS J 4 4 NM1 NM2 "nmos",W/L=40/2.5vss "nmos",W/L=40/2.5 VSS VSS NM3 "nmos",W/L=80/2.5 两级开环比较器的电路原理图 HSPICE的网表文件(附带文件: ) 2. 根据1中比较器电路拓扑结构可以编写以下的网表文件如下: ************************comparator************************* *************************netilst*************************** mp1IblasIblasvddvddpmosl=w=25u mp21 mp3out2 mp42 mp5out1 mn12 Iblasvddvddpmosl=w=25u lblasvddvddpmosl=w=25u In1 In2 11pmosl=w= 11pmosl=w= gndgndnmosl=w=40u gndgndnmosl=w=40u gndgndnmosl=w=80u *************************endnetilst*********************** mn2out1 mn3out2 out1 Title ******************llbrary********************************** .inelude"C: \synopsysWhspicenetllst\" ******************endllbrary****************************** Slze B Date: Flle: 5 Numbf 29-Jun- C: \DoCL VDDvddgndDC5 IBIblasgndDC30u .OPvin1in1gndpulseOnOnOn100n200n)vin2in2gnddc .tran1n400n.probe .end 3.HSPICE的模拟结果(附带文件: ) 红色曲线: 黄色曲线: 橙色曲线: 60ns,下降时延大约为40ns,总的时延平均为50ns. in2端输入信号in1端输入信号out2端输出信号由此波形图可以看出: 上升时延大约为: 虽然,性能不是很理想,但功能是基本实现了;可以进一步优化。 4.参数确定 最终确定的参数为: 五.比较器的物理版图设计 1.编辑比较器的原理图(附带文件为)利用IC工具软件可以编辑比较器的原理图如下: 2.据编辑比较器的版图(附带文件: 和) (1)总的比较器版图几何结构如下图所示 左上: 右上: 左下: 右下: 亠: 希: 寸工二一好 亠小鶴■•先 MP4和MP5 MP1、MP2和MP3 MN1和MN2 MN3 (2)总体布局规划一方面,从电路的电气可靠性考虑, 響……一二 1*」 沁「 •」k-二•Fa ■: -.W: H・ ■■■--■«1-■r ■IT--- : : 4“ 一-亠. 誉: —恋赭=4WES 把输入差分放大管 Ki」 MP4和MP5和输出的MN3布 局成对角线方位,可以减少输出对输入的干扰;另一方面,从电路的几何面积考虑,把MP1、MP2和MP3分别拆成两条长为的栅,把MN1和MN2分别拆成两条长为20um的栅,把MN3拆成4条长为20um的栅,并按上图布局可以使整个版图紧凑面积最小。 (3)MOS晶体管的匹配 由于MP4和MP5的宽长比不是很大,没有拆分,所以把他们平行并排对称布图匹配;MP1、MP2和MP3分别拆成两条长为的栅,并把MP1排在中间,MP2和MP3分别排在它的两侧;MN1和MN2分别拆成两条长为20um的栅,并按共质心方式布图匹配。 ⑷大尺寸MOS晶体管的处理 MN3的宽长比高达80/,把它拆分成4条长为20um的栅,单管版图几乎正方形。 ⑸在DRC检查 由于事先较为详细的理解了中微晶圆电子有限公司”的《SPTMCOMSPROCESSDESIGN RULES内容,布图过程程中,尽可能根据它来取相应部分的尺寸,因此布图过程中没有太多的DRC错误。 但是这里必须提到一个失误,由于疏忽,误以为contact到poly栅的间距大 于,并且以此为准先画源和漏区金属时都没有打contact,等到最后打contact并做DRC检查 时,此问题暴露了,最后由于时间太紧,只好修改的文件,强行把这约束改为,结果DRC 检查没有错误。 可是,如果流片这是万万不可的,因为工艺决定了DRC的约束,这里讲述 的这种做法也是不允许的,只是时间太紧了(版图我画到凌晨4: 38)才如此操作,不过正 确的方法因该是: 把contact到poly栅的间距调大到。 通过这问题,我也吸取教训: 不可以最后打contact否则易出错;还是得认真。 3.整体DRC检查及其结果(附带文件: )DRC最后检查结果如文件所述如下图所示: 常LUUto/C-JCkTO HW'iCfrRMLHICE-HEnfVLIST]J*.-*****™EcI\■>F料NTE皿店DffHFCiVSC-E-IPPUTL^JjfFiJDSIISTIDC- •Zs.ilKA.rAloiddpiJ-aA^iak'inlist=cov/gd: ■丄t? >EOTi 血暉-err.c斟 iIf-=dicaut 'r: pcvKiu-^L--/£Kdenfev*^old/dt^luIb/bii-? DRC错误列表空,可见没有DRC错误。 4.LVS检查及其结果(附带文件: LVS佥查结果如文件所述,如下图所示: miMERHinn: ERmintERiromER OF OF OP PW-HATCHEDim-HATCUEDMATCHEDWATCHED ■l.J**耳*F LATIOUT

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 两级 开环 比较 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx

人力资源总监高端沙龙活动参加人员名单表格文件下载.xls

人力资源总监高端沙龙活动参加人员名单表格文件下载.xls