简单的CPU设计.docx

简单的CPU设计.docx

- 文档编号:10443436

- 上传时间:2023-02-11

- 格式:DOCX

- 页数:19

- 大小:229.68KB

简单的CPU设计.docx

《简单的CPU设计.docx》由会员分享,可在线阅读,更多相关《简单的CPU设计.docx(19页珍藏版)》请在冰豆网上搜索。

简单的CPU设计

CPU设计

10计算机科学与技术

姓名:

谢xx

学号:

201040200xx

一.非常简单的CPU设计规范:

1.确定CPU的用途:

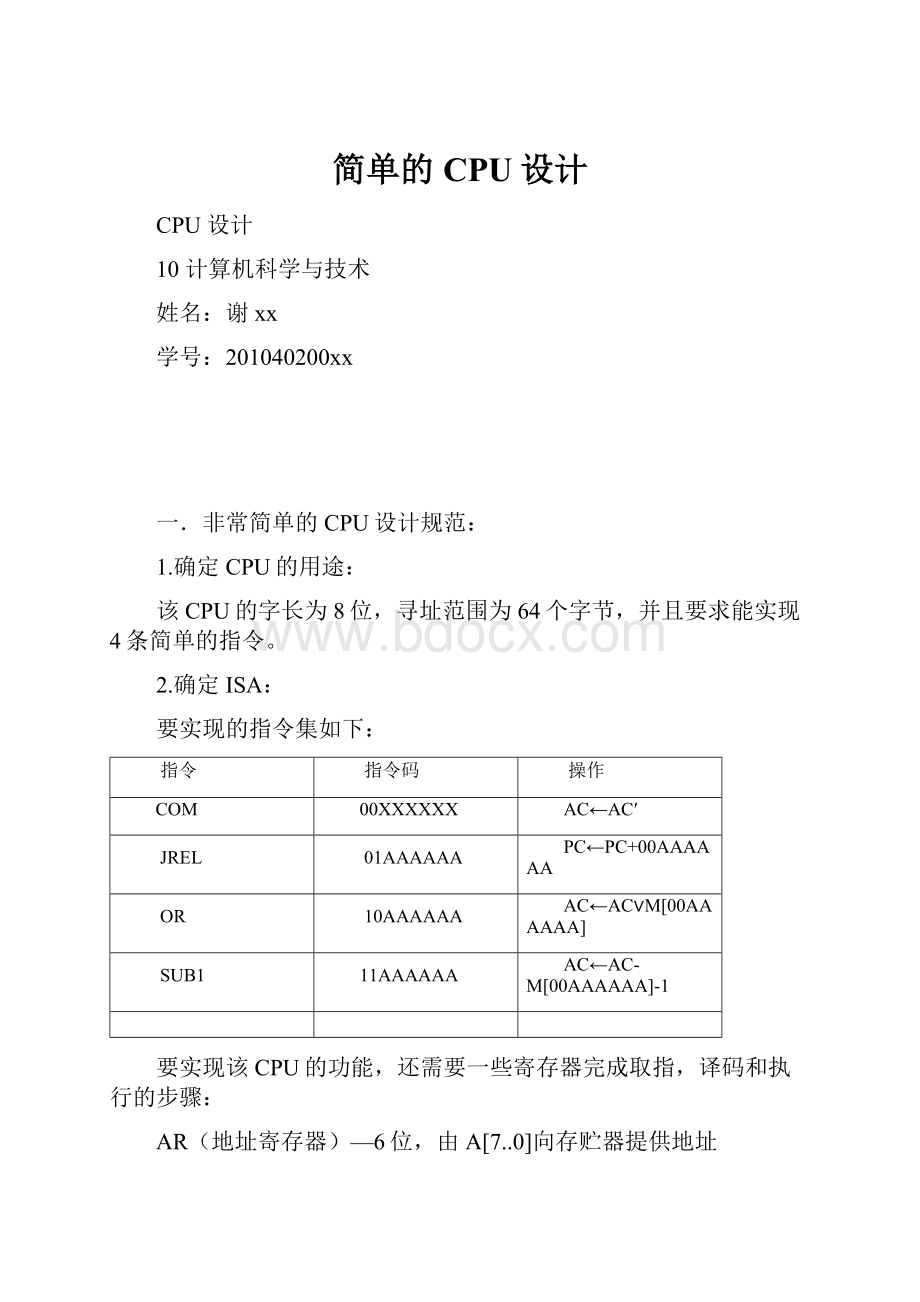

该CPU的字长为8位,寻址范围为64个字节,并且要求能实现4条简单的指令。

2.确定ISA:

要实现的指令集如下:

指令

指令码

操作

COM

00XXXXXX

AC←AC′

JREL

01AAAAAA

PC←PC+00AAAAAA

OR

10AAAAAA

AC←AC∨M[00AAAAAA]

SUB1

11AAAAAA

AC←AC-M[00AAAAAA]-1

要实现该CPU的功能,还需要一些寄存器完成取指,译码和执行的步骤:

AR(地址寄存器)—6位,由A[7..0]向存贮器提供地址

PC(程序计数器)—6位,指出下一条指令的地址

DR(数据寄存器)—8位,通过D[7..0]从存贮器接收指令和数据

IR(指令寄存器)—2位,存放从存贮器中取回的指令的操作码部分

3.为CPU设计状态图:

为了确定CPU的状态图,需对每条指令作如下分析:

①从存贮器中取指令

②指令译码

3指令执行

二.从存贮器中取指令:

⑴原理:

根据冯•诺依曼型的原理(指令在存贮器中顺序存放••••••),在CPU能执行指令之前,它必须将这条指令从存贮器中取出,CPU通过执行如下的操作序列完成这个任务:

1选择存贮单元由A[5..0]确定

2对A[5..0]译码、延迟并向存贮器中发一个信号,使存贮器将此指令输出到它的输出引脚。

这些引脚与CPU的D[7..0]相连接。

CPU从这些引脚读入数据。

⑵具体的操作

①要取的指令的地址存放在程序计数器(PC)中。

由于A[5..0]从地址寄存器AR中。

这样,取指令周期的第一个状态就是:

FETCH1:

AR←PC

这一状态的意义是当FETCH为真时,把PC的值送到AR,执行微操作AR←PC,以下同理。

②CPU必须存贮器中读取指令。

为此CPU必须发一个READ信号到存贮器的RD端使存贮器将数据送到D[7..0]上。

同时,CPU读进该数据并放到DR中,因为DR是用来访问存贮器的唯一寄存器。

同时还实现微操作PC←PC+1,为取下一条指令作准备。

FETCH2:

DR←M,PC←PC+1

③作为取指令的一部分,CPU还必须完成两件事。

•DR的高2位拷贝到IR,母的是确定指令的功能(即将指令的操作码读入IR)

·DR的第六位拷贝到AR。

FETCH3:

IR←DR[7..6],AR←DR[5..0]

图1-1CPU的取指周期

三.指令译码:

由于本CPU只有四条指令,用不同的IR的值来确定四个不同的执行周期:

四.指令执行:

1.COM指令

COM1:

AC←AC′;将AC取反,再将结果送回AC中。

(在AC的数字电路中实现AC的取反操作)

2.JREL指令

该指令操作码为01AAAAAA,即是将PC加上AAAAAA再送回到PC。

JPEL1:

PC←PC+DR;数据寄存器DR和PC的数相加,并把结果存回PC中。

3.OR指令

要完成该指令,CPU要做两个步骤:

OR1:

DR←M;从存贮器取出一个操作数送到数据寄存器中(M的地址是由A[5..0]确定的)

OR2:

AC←AC∨DR;数据寄存器DR和AC的数做或操作,并把结果送回AC中。

4.SUB1指令

SUB1指令的执行周期与OR指令相类似,同样也要两个步骤:

SUB11:

DR←M;从存贮器取出一个操作数送到数据寄存器中

SUB12:

AC←AC-DR-1;将AC中的数减去数据寄存器DR再减去1,并把结果放回AC中。

综上,可以得到CPU的完全状态图:

图1-3CPU的完全状态图

五.建立所需要的数据通路:

1.与CPU的每个状态相关联的微操作(共9个状态)

FETCH1:

AR←PC

FETCH2:

DR←M,PC←PC+1

FETCH3:

IR←DR[7..6],AR←DR[5..0]

COM1:

AC←AC′

JPEL1:

PC←PC+DR

OR1:

DR←M

OR2:

AC←AC∨DR

SUB11:

DR←M

SUB12:

AC←AC-DR-1

2.建立数据通路的原理和方法

存贮器数据通路的原理:

1存贮器是通过引脚D[7..0]将数据送给CPU的8位内部总线。

2存贮器的地址确定是通过地址引脚A[5..0]和D[7..0]通路,如图1-3:

图1-3CPU初步的寄存器部分

CPU的内部数据通路:

该CPU的内部数据通路采用在总线的方式,有利于满足各种寄存器数据交换的需要,减少数据通路。

3.CPU内部寄存器控制信号的定义和确定方法

1).原理:

首先把各种操作重新分组,依据是把修改同一个寄存器的操作分配在同一组。

本CPU共有九种状态,五个寄存器的分配情况如下:

AR:

AR←PC;AR←DR[5..0]

PC:

PC←PC+1;PC←PC+DR

DR:

DR←M

IR:

IR←DR[7..6]

AC:

AC←AC′;AC←AC∨DR;AC←AC-DR-1

2).决定每个部件应完成的功能

1AR,DR,IR

这三个寄存器总是从其他一些部件中装入数据。

若数据已在总线上,则需要做的就是能够执行并行装入操作。

(它们各自的LD端分别由ARLOAD,DRLOAD,

IRLOAD信号同步装入)

2PCAC

这两个寄存器能从其他一些部件中装入数据。

还有自增当前值。

所以应创建一个单独的硬件使之能自增当前值。

4.把每个部件都连接到系统总线上

三态缓冲区—原有的寄存器总是在结果准备好后立即输出到系统总线,造成多个结果同时输出到系统总线的可能性出现,是CPU内部数据可能发生冲突。

所以应增加三态缓冲区加以控制。

但AR的输出还应与A[5..0]相连,这是寻址所需。

5.根据实际需要修改图4的设计,并加上适当控制信号

1).AR:

仅仅向存贮器提供数据(地址),没有必要将它的输出

连接到内部总线上。

(

可删除)。

加上

ARLOAD实现BUS装入数据。

图中CLK是CPU核心时钟

2).AR←PC:

保留三态缓冲器有PCBUS控制同步

3).IR:

不通过内部总线向任何其他部件提供数据(所以

可删除)而IR的输出将直接送到控制器用于确定指令的功能(见图5,LD,在FETCH3为真时载入)

4).AC:

本CPU不向其他任何寄存器提供数据(

可删除)

5).D[7..0]:

各部件所需要的数据不统一。

显然,从存贮器读出的数据为8位,有写不加需要8位D[7..0](如DR、AC),而有些部件只需6位D[5..0](如AR、PC),还有些部件只需2位D[7..6](如IR),必须确定哪些寄存器从总线的哪些为上接收和发送数据。

对于DR寄存器来说应该由DRBUS实现同步。

DRLOAD实现LD(载入)。

6).AC:

必须能装载AC∨DR,AC←AC′,AC-DR-1的结果。

CPU必须包含一个能产生这些结果的ALU(算术逻辑运算器)并由ACLOAD实现装入。

图5

至此,问题的关键是设计适当的ALU。

六.ALU的设计

1.ALU数据通路分析

ALU必须能接收AC、PC和DR作为输入,然后把运算结果输出到AC和PC。

2.实现运算功能

⑴在本CPU中,把AC的导线和ALU的输入输出连接起来,并且利用系统总线把PC、DR和ALU的输入连接起来。

⑵非常简单ALU的设计

1问题:

ALU必须能完成以下四个运算:

AC←AC∨DR

PC←PC+DR[5..0]

AC←AC′

AC←AC-DR-1

2解决办法:

设计一个部件算术运算AC←AC-DR-1和PC←PC+DR[5..0],另一个部件完成逻辑运算AC←AC∨DR,AC←AC′。

并且用一个多路选择器从正确的输出中选择数据送入AC或PC。

3具体设计

a.算术运算

对AC←AC-DR-1进行改写,得

AC←AC+DR′//求反加1,即把减法变为加上该数的补码。

PC←PC+DR[5..0]把PC和DR的低六位输送到ALU,进行加法运算,再送回到PC。

b.逻辑运算

用一个2选1多路开关选择取反(AC′)或逻辑或(AC∨DR)

c.用一个2选1确定输出逻辑运算或算术运算结果控制信号:

ALUS2

d.非常简单ALU逻辑电路图6

图6一个非常简单的ALU

4.用硬布线方法设计控制器

本CPU采取用时序逻辑和组合逻辑来产生控制信号的方法来设计控制器

一、非常简单CPU的控制器

1.组成包含三部分

1计数器:

保存当前状态

2译码器:

接受当前状态并为每个状态生成单独的信号

3逻辑组合:

接受单独的状态信号,为每一个部件生成控制信号以及计数器的控制信号(反馈)

2.硬布线控制单元原理图(图7)

图7一般硬布线控制原理图

3确定计数器的位数

共有9个状态。

(四条指令,共有9个状态)

需要一个四位计数器和一个4-16位译码器。

二、计算器和译码器的设计

1.FETCH1状态(公操作)

规定为计数器的0值,使用计数器的CLR=1(清零有效)到达这一状态。

当CPU的任一条指令执行完毕,CPU一定转入取指令状态。

2.将顺序状态设定为计数器的连续值,用INC(自增1)实现。

本CPU各个状态对应的值:

FETCH1赋值为计数器值0

FETCH2赋值为计数器值1

FETCH3赋值为计数器值2

COM1赋值为计数器值8

JPEL1赋值为计数器值10

OR1赋值为计数器值12

OR2赋值为计数器值13

SUB11赋值为计数器值14

SUB12赋值为计数器值15

3.确定一个每个执行周期中的第一个状态

根据映射函数1IR[1..0]0确定指令周期的入口:

1000(8)---COM

1010(10)---JPEL1

1100(12)---OR1

1110(14)---SUB11(见图7)

图8非常简单CPU的硬布线控制器

4.计数器LD、INC、CLR控制信号的确定

LD:

其函数为LD=FETCH3

INC:

其函数为

INC=FETCH1+FETCH2+OR1+SUB11

对应的逻辑电路为

CLR:

其函数为

CLR=COM1+JPEL1+OR2+SUB12

对应的逻辑电路为

三、根据译码器的输出信号经组合后产生CPU中寄存器的有关控制信号用于控制AR,PC,DR,IR,M,ALU及缓存器。

1.ARLOAD

因为在FETCH1中要实现AR←PC

FETCH3中要实现AR←DR[5..0]

2.PCLOAD,PCINC

PCLOAD=JPEL1

PCINC=FETCH2

3.DRLOAD(实现DR←M)

DRLOAD=FETCH2+OR1+SUB11//JPEL1不需要装载,因为直接PC←PC+DR

4.ACLOAD(实现AC←AC′,AC←AC∨DR,AC←AC-DR-1)

ACLOAD=COM1+OR2+SUB12

5.IRLOAD

IRLOAD=FETCH3

6.ALUSEL

ALU有两个控制输入信号—ALUS1,ALUS2

当ALUS2=0时,输出和

当ALUS2=1且ALUS1=1时输出逻辑或

当ALUS2=1且ALUS1=0时输出取反结果

因为JPEL指令不会用到AC,故当执行JPEL指令时,由于ACLOAD=0所以AC并没有装载ALU中的值

当执行SUB12指令时,ALUS2=0,ALU直接输出和

当执行COM指令时,ALUS1=0且ALUS2=1,ALU输出取反结果

当执行OR2指令时,ALUS1=1且ALUS2=1,ALU输出逻辑或

7.缓冲器控制信号

MENBUS=FETCH2+OR1+SUB11

PCBUS=FETCH1+JPEL1

READ=FETCH2+JPEL1+OR1+SUB11

DRBUS=FETCH3+JPEL1+OR2+SUB12

至此,CPU设计完成,下面是设计验证:

1.程序段描述如下【存贮单元:

指令】

0:

COM功能AC←AC′

1:

JPEL4功能PC←PC+M[4]

2:

OR5功能AC←AC∨M[00AAAAAA]

3:

SUB14功能AC←AC-M[00AAAAAA]-1

4:

00H

5:

10H

备注:

默认AC的初始值为FFH;

2.根据CPU的状态图可知各条指令执行的状态顺序如下:

COM:

FETCH1→FETCH2→FETCH3→COM

JPEL:

FETCH1→FETCH2→FETCH3→JPEL1

OR:

FETCH1→FETCH2→FETCH3→OR1→OR2

SUB1:

FETCH1→FETCH2→FETCH3→SUB11→SUB12

3.执行跟踪

非常简单CPU执行COM指令的工作原理描述如下:

指令功能是AC←AC′,即是把原AC中的值取反后再送回AC中

1在FETCH1状态,把PC=0的现行值送AR,硬布控制器发出PCBUS、ARLOAD便能实现AR←PC

2在FETCH2状态,为实现DR←M[0],PC←PC+1,控制器发出READ、MEMBUS、DRLOAD、PCINC

3在FETCH3状态,为实现IR←DR[7..6],AR←DR[5..0],控制器应发出DRBUS、IRLOAD、ARLOAD

4COM状态,将AC中的值取出后,对其取反在送入AC,控制器应发出ACLOAD、ALUS1、ALUS2

至此COM指令执行完毕,返回准备取出下一条指令的FETCH1状态

其余指令的执行情况见下表:

指令

状态

有效信号

所执行的操作

次态

COM

FETCH1

PCBUS,ARLOAD

AR←0

FETCH2

FETCH2

READ,MENBUS,

DRLOAD,PCINC

DR←00H,PC←1

FETCH3

FETCH3

DRBUS,ARLOAD,

IRLOAD

IR←00,

AR←00H

COM

COM1

ALUS1,ALUS2=0

ACLOAD

AC←00H

FETCH1

JPEL

FETCH1

PCBUS,ARLOAD

AR←1

FETCH2

FETCH2

READ,MENBUS,

DRLOAD,PCINC

DR←44H,PC←2

FETCH3

FETCH3

DRBUS,ARLOAD,

IRLOAD

IR←01,

AR←04H

JPEL1

JPEL1

PCLOAD,MENBUS

READ

PC←PC+04H

FETCH1

OR

FETCH1

PCBUS,ARLOAD

AR←2

FETCH2

FETCH2

READ,MENBUS,

DRLOAD,PCINC

DR←85H,PC←3

FETCH3

FETCH3

DRBUS,ARLOAD,

IRLOAD

IR←10,

AR←05H

OR1

OR1

DRLOAD,MENBUS

READ

DR←10H

OR2

OR2

ACLOAD,ALUS2=0

ALUS1=0

AC←00H∨10H=10H

FETCH1

SUB1

FETCH1

PCBUS,ARLOAD

AR←3

FETCH2

FETCH2

READ,MENBUS,

DRLOAD,PCINC

DR←C4H,PC←4

FETCH3

FETCH3

DRBUS,ARLOAD,

IRLOAD

IR←11,

AR←04H

SUB11

SUB11

DRLOAD

DR←00H

SUB12

SUB12

ACLOAD,ALUS2

AC←10H-00H-1=01H

FETCH1

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 简单 CPU 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx