小数分频频率合成器理论基础翻译.docx

小数分频频率合成器理论基础翻译.docx

- 文档编号:1041284

- 上传时间:2022-10-15

- 格式:DOCX

- 页数:12

- 大小:404.27KB

小数分频频率合成器理论基础翻译.docx

《小数分频频率合成器理论基础翻译.docx》由会员分享,可在线阅读,更多相关《小数分频频率合成器理论基础翻译.docx(12页珍藏版)》请在冰豆网上搜索。

小数分频频率合成器理论基础翻译

小数分频频率合成器的理论基础

A.Marques_,M.SteyaertandW.Sansen

ESAT-MICAS,K.U.Leuven,Kard.Mercierlaan94,B-3001Heverlee,Belgium

本文提出了一种基于锁相回路(PLL)频率合成器的演变概述。

数字PLL的主要限制的描述,以及随之而来的小数N技术使用的必要性是有道理的。

合成频率的旁瓣典型的杂散噪声线的起源进行了解释。

它通过使用数字∆∑调制器来控制分频值展示了如何消除这些杂散噪声线。

最后,数字∆∑调制器的使用同分数N PLL的输出相位噪声的影响一起进行了分析。

1.介绍

无线通信领域,在过去十年中有了很大的发展。

这种快速发展,主要是通过引进强大的数字信号处理技术。

这些技术允许执行复杂的调制解调方案,以及先进的数字校正技术,最终产生非常高性能的系统,可以完全或几乎完全集成在一个标准的低成本技术。

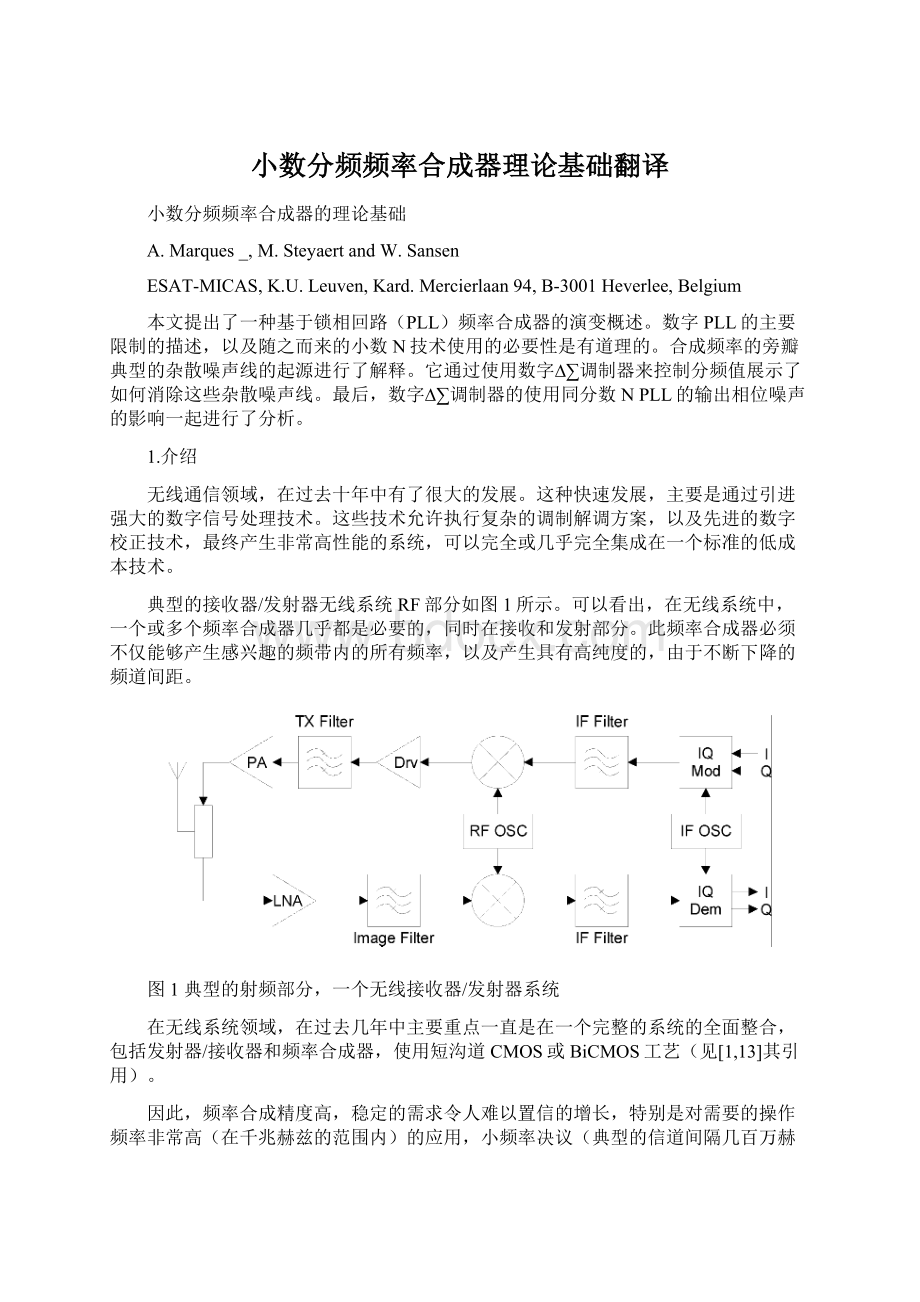

典型的接收器/发射器无线系统RF部分如图1所示。

可以看出,在无线系统中,一个或多个频率合成器几乎都是必要的,同时在接收和发射部分。

此频率合成器必须不仅能够产生感兴趣的频带内的所有频率,以及产生具有高纯度的,由于不断下降的频道间距。

图1典型的射频部分,一个无线接收器/发射器系统

在无线系统领域,在过去几年中主要重点一直是在一个完整的系统的全面整合,包括发射器/接收器和频率合成器,使用短沟道CMOS或BiCMOS工艺(见[1,13]其引用)。

因此,频率合成精度高,稳定的需求令人难以置信的增长,特别是对需要的操作频率非常高(在千兆赫兹的范围内)的应用,小频率决议(典型的信道间隔几百万赫兹数100千赫),和低相位噪声数字(100dBc的订单数100千赫载波)。

此外,同时,在过去几十年,数字可编程的频率合成器的需求也增加了。

本文提供了一个数字可编程频率合成器相位锁定回路(PLL)为基础的演变概述。

由于相位噪声实际上是为无线通信系统所要求的规格是非常艰难的,主要的重点将在相位噪声的分析和如何在不削弱系统的其他特征的同时减少它。

下面的思想将是这些结构将被期望用在高频无线系统,并完全或几乎完全集成成本低,技术标准(如尽可能短通道数字CMOS技术)。

第2节中,我们提供了动机研究基于PLL可编程频率合成,提出不久在其他的替代品存在一定的局限性。

第3节中,众所周知的数字锁相环介绍,这种结构的主要限制。

在第4节,小数N分频PLL原理解释,结构最重要的问题是确定的。

因此,在第5条,该方法在[7,11]开发实现小数N使用Δ-Σ调制器的功能进行了探讨。

最后,在第6条,得出了一些结论有关这些技术的探索。

2.频率合成技术

有几种可能的频率合成技术。

最常用的方法是:

第一,直接模拟合成;第二,直接数字合成;第三,基于PLL结构的间接合成[4,6,12]。

直接模拟合成,如图2所示,硬件密集的技术,使一个实现精细的频率分辨率和快速开关时间。

然而,这种技术不适合高频的和传统的CMOS低相位噪声合成(或BiCMOS工艺)技术。

事实上,集成度实现这种技术是相当减少,产生的结果实现起来非常昂贵。

图2直接合成技术的原则

直接数字合成,在图3中,提供如直接模拟合成技术,精细的频率决议和快速开关时间。

它也可以完全在一个标准的CMOS技术下实施这项技术,。

此外,通过一个相对简单的修改相位累加器的结构,它甚至还提供了一个简单的方式实现直接的相位和频率调制在一个成本稍高的芯片面积上。

然而,对于典型的无线应用需要高频率和低相位噪声,硬要求DAC的时钟频率上,决议,非线性性和毛刺能量的使用这项技术是不可能的。

图3直接数字合成技术

间接的合成,如图4所示,是比较与前两次的技术,更适合高频率的正弦信号的合成。

此外,可以集成合成器的主要组成部分在BiCMOS或即使在CMOS技术。

电压通常主要控制振荡器(VCO)构成整合的问题。

但是,目前它也有可能集成这个模块在一个标准的CMOS技术之上,即使在千兆赫兹的频率范围内操作和实现了非常低的相位噪声的数字[3,8,9,14]。

图4数字锁相环

这种技术的主要问题导致合成过程中的间接性质。

首先,由于参数是一个非常低的频率信号相对合成信号,在频带参数相位噪声等于PLL显示输出乘以一个大因数(频率乘以分频系数为100增加了带内参数相位噪声40分贝)。

第二,低频率参考信号要求PLL环路带宽更小,因此产生固有的缓慢切换结构。

然而,这一问题已逐步得到解决,终于在一个小数分频PLL控制合成由Δ-Σ结构,整合一个标准的CMOS技术,适合高频率和低相位噪声,并取得了良好的频率分辨率和短的开关时间。

为总结此频率合成的简要概述技术,表1比较几个关于超大规模集成电路集成无线解决方案最重要的几个方面的技术指标。

表1比较不同的合成技术。

技术

频率范围

相位噪声+毛刺

频率精度

转换时间

集成度

直接模拟

低

好

好

非常快

小型

直接数字

低

不好

好

非常快

全部

集成PLL

高

好

折中

全部

FractPLL

(ΔΣ控制)

高

不好

好

快

全部

因此,高频率的稳定性和准确性,低相位噪声和高频率合成能力,似乎是唯一真正的选择是PLL[5,12]。

高频率操作的需求和需要锁定环路到一个相对较低的频率参考结合使用数字模块的简单做数字锁相环,数字分频器和数字鉴相器,非常有吸引力的(见图4)。

在下一节将分析这种结构。

3.数字式锁相环

由于所需的高稳定性和低噪声输入信号,这个环路可以作为线性控制分析系统,输入和输出信号是相位的[4,6]。

系统框图如图5所示。

图5,我们马上就可以得出这样的结论锁定条件下(频率和相位误差,等于零),输出频率由下式

fo=N·fr

(1)

图5一个数字PLL的框图

请注意,生成的输出可控制编程分频器的N值。

但是,N为一个整数值,第一个限制立即出来:

频率分辨率等于参考频率。

从参考噪声的噪声传递函数源和输出的VCO噪声,分别给出

(2)

(3)

由于环路滤波器H(S),具有低通特性,将参考源的相位噪声低传递给输出和乘以N,而相位噪声VCO的将是高传递到输出,造成噪音环路带宽之外的组件不衰减。

因此,输出相位噪声约为等于向参考源的相位噪声乘以N在频率低于环路带宽下,或等于VCO的相位噪声在频率高于环路带宽下。

给一个确定的的参考频率,优化循环的特性,以实现低输出相位噪声是不是一件简单的事情,因为:

·首先,为了减少由参考频率的噪音产生的输出相位噪声的贡献,我们应该减少环路带宽,并选择参考源的相位噪声低的特点。

自从对于一个循环顺序两极将接近的位置,但随后该系统的建立时间会加重,环路的稳定性将产生更多的问题。

·其次,要降低VCO的输出贡献相位噪声,我们应该增加环路带宽设计了一个非常低的噪声VCO。

但随后的抑制参考频率的噪音会更小,这意味着可能是一个更高的顺序循环,如果环路带宽和参考频率过于接近,或增加一个参考频率,这是很难设计的。

因此,如果低相位噪声要求覆盖很宽的频率波段,我们必须建立一个折中相位噪声接近并远离合成频率,参考频率抑制和回路的开关时间。

由于在数字锁相环频率分辨率是直接依赖于参考频率,它时下很难甚至是不可能实现这种结构频率分辨率,开关和相位噪声要求的电信市场的要求。

4.N分频锁相环

N分频锁相环是一个数字锁相环分频值随时间函数变化。

通常用作频率双模预定标器的分频器,两个数字除以,说N1和N2(N2> N1)。

为了锁定VCO在一个小数参考频率的整数倍,我们划分小数部分,它可以在统计方法划分有时由N1和有时由N2。

所需的分频的定义通常是做一个累加器,应用一个数字N(),然后用溢出标志使用控制分频值,应使用。

该块系统框图如图6所示。

图6N分数锁相环

如果我们约定没有溢出值是N1时,有一个溢出值是N2,然后我们得到立即得到

(4a)

我们也可以表达在输出频率或,定义我们将得到

(4b)

请注意,分频器是不是在事实上除以在每个周期的分数值的输出频率。

相反,它在每个周期除以一个整数,除以分数值仅以统计方法,会产生输出噪声决定于选定依赖频率。

图7N分数锁相环相位误差校正

事实上累加器作为相位累加器。

要理解这一点,认为环路锁定时,目前累加器的值是不同于零且没有溢出。

然后,VCO的输出频率被分为N1,因此将高于参考频率。

在每个参考周期相位检测比较,例如,两个低到高的转变信号。

因此,相位检测器输出电压将增加每一个周期。

累加器值同时也是增加到一。

当累加器的值达一,溢出和分度值变为N2。

现在,分为输出频率低于参考频率,然后之间的相位差两个信号的下降。

这种周期性的条件下锁定行为会不断重复并且相位检测器输出将与累加器值成正比(见图8)。

因此,我们可以得出结论,在累加器的值代表两个信号之间的相位误差的比较。

从图8可以看出,相位检测器输出具有周期性的锯齿形电压,频率等于。

显然,这锯齿波信号会诱发相位噪声VCO的输出,主要尖峰密切在频率偏移的多个所需的频率。

图8相位检测信号(N1、N2分别为4、5,n为0.1)

显然,如果这个分数频率落在环路带宽,将产生非常大的尖峰过滤的锯齿波信号。

但是,如果这个分频比PLL带宽高得多,他们会大力减少循环过滤作用

理论上,它可以完全删除它们,因为我们知道信号之间的相位差适用于相位检测器。

我们可以应用累计DAC的相位误差,正确缩放值和减去相位检测器输出。

这种技术被称为相位插补和结合它构成一个DAC的模拟相位内插系统(API),[12]。

系统框图图7。

参照图8,我们可以看到,最大相不同的是等于VCO频率的一个周期,N2-N1的周期一般。

由于VCO的频率是变量,最大相差幅度相位误差信号是依赖于合成频率。

假设输出没有相位噪声,最大相位差(),振幅相位误差信号(),以及必要的比例因子(A)(假设累加器之间有一个规范化的输出0和1),可以立即计算:

(5)

(6)

因此:

(7)

这是本合成器的主要问题。

我们即不补偿相位误差锯齿形,接受每个多相位噪声杂散尖峰在每一个,也不用尝试以补偿相位误差,设计非线性DAC的输出增益系数匹配相当敏感。

这种复杂性方法,以及相关的成本,它只适合高性能设备,在特定的测试设备。

5.Δ-Σ锁相环

这是一个简单的问题,认识到累加器事实上是一阶的ΔΣ调制器。

输出频谱位流的ΔΣ调制器包含一个直流分量等于应用的m值,还有寄生噪声线,所谓的模式噪声[2]。

因此,这种寄生噪声线将被转移到输出,并会出现以及定义在旁瓣穗线周围的合成频率。

这是人所共知的,为ΔΣ调制器的模式噪声具有常数输入的信号是非常高的,因为输入信号和量化之间的高度相关噪音。

这也是众所周知的,二阶和高阶ΔΣ调制器表现出输入信号之间的相关性较低量化噪声,几乎消除模式噪音。

所以,如果我们取代了二阶累加器或高阶ΔΣ调制器,像图9描述,似乎自然地想到在合成频率中更好的相位噪声特性。

图9ΔΣN分数PLL

对于这个系统,我们可以计算出的相位噪声由于使用的小数除法合成信号技术。

基于线性/白噪声模型,给出合理结果为第二和高阶调制器[2]的ΔΣ调制器的输出

(8)

其中n表示现在调制器的阶数m(Z)和E(Z)分别为输出比特流的Z-变换和量化噪声,。

现在,我们可以计算的ΔΣ调制器的使用效果分频器输出相位噪声假设一个理想的VCO。

分频给予

(9a)

对于符号的简化,让我们定义。

考虑频率偏差频率都很小,我们可以近似为

(9b)

因此,从所需的频率,频率偏差给予

(10)

使用单端功率谱密度(PSD)代替并注意到,量化步长等于2(调制器输出始终为1),我们得到,因此PSD频率偏差相位噪声(参见(A.6)),分别由

(11)(12)

这个阶段的噪声引起的相位

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 小数 分频 频率 合成器 理论基础 翻译

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls