嵌入式设计课设论文参考ARM实验箱指导书.docx

嵌入式设计课设论文参考ARM实验箱指导书.docx

- 文档编号:10349030

- 上传时间:2023-02-10

- 格式:DOCX

- 页数:259

- 大小:2.31MB

嵌入式设计课设论文参考ARM实验箱指导书.docx

《嵌入式设计课设论文参考ARM实验箱指导书.docx》由会员分享,可在线阅读,更多相关《嵌入式设计课设论文参考ARM实验箱指导书.docx(259页珍藏版)》请在冰豆网上搜索。

嵌入式设计课设论文参考ARM实验箱指导书

第1章EL-ARM-830实验系统的资源介绍

ARM实验箱硬件资源概述

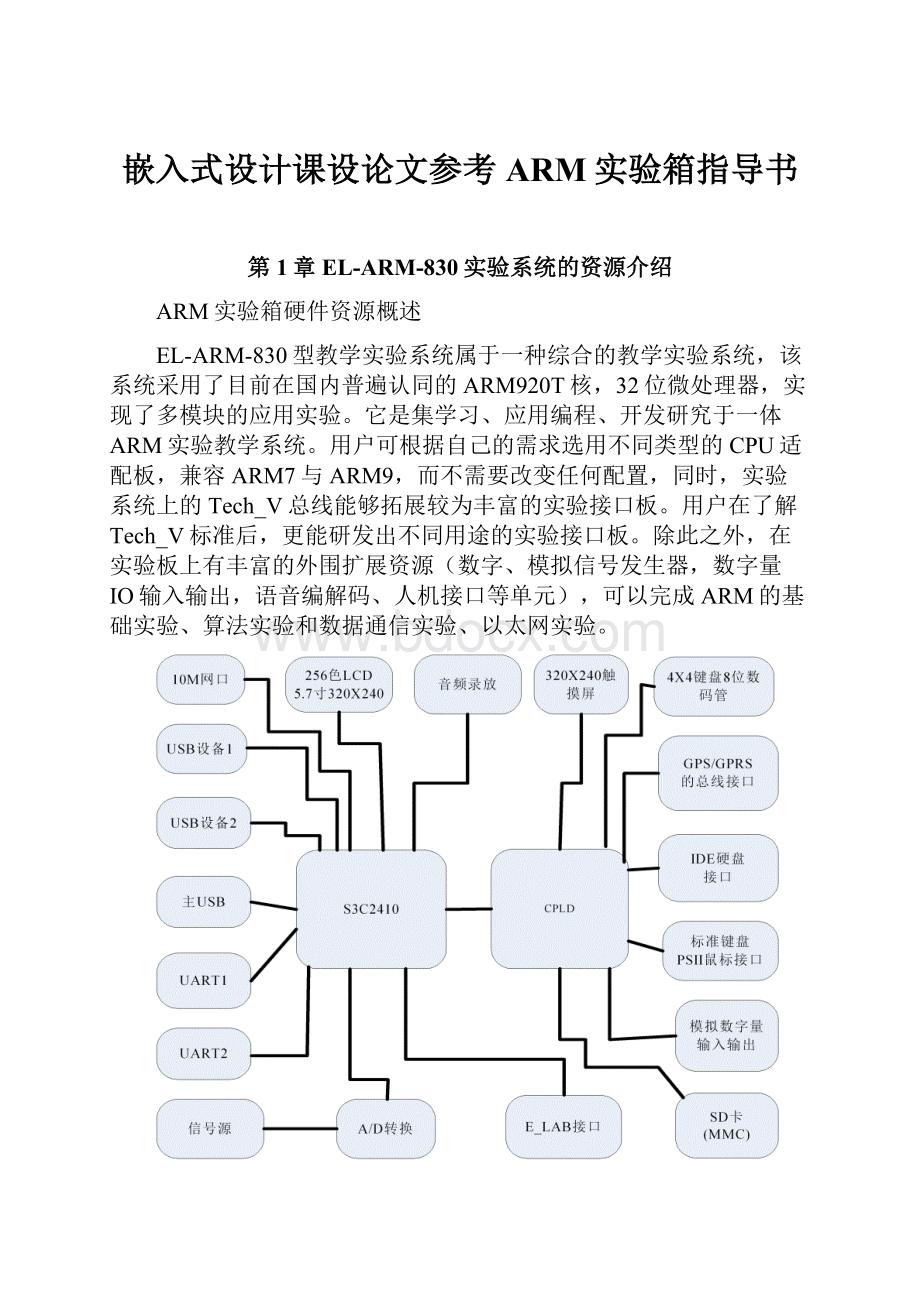

EL-ARM-830型教学实验系统属于一种综合的教学实验系统,该系统采用了目前在国内普遍认同的ARM920T核,32位微处理器,实现了多模块的应用实验。

它是集学习、应用编程、开发研究于一体ARM实验教学系统。

用户可根据自己的需求选用不同类型的CPU适配板,兼容ARM7与ARM9,而不需要改变任何配置,同时,实验系统上的Tech_V总线能够拓展较为丰富的实验接口板。

用户在了解Tech_V标准后,更能研发出不同用途的实验接口板。

除此之外,在实验板上有丰富的外围扩展资源(数字、模拟信号发生器,数字量IO输入输出,语音编解码、人机接口等单元),可以完成ARM的基础实验、算法实验和数据通信实验、以太网实验。

图1-1-1EL-ARM-830实验教学系统的功能框图

1.1实验系统的硬件资源总揽

☆ CPU单元:

内核ARM920T,芯片三星的S3C2410,工作频率最高202MHz;

☆ 动态存储器:

64MB,芯片HY57V561620;

☆海量存储器:

32MB,芯片K9F5608;

☆USB单元:

1个主接口,两个设备接口,芯片PDIUSBD12;

☆网络单元:

10/100M以太网,芯片AX88796;

☆UART单元:

2个,最高通信波特率115200bps;

☆语音单元:

IIS格式,芯片UDA1341TS,采样频率最高48KHz;

☆LCD单元:

5.7寸,256色,320X240像素;

☆触摸屏单元:

四线电阻屏,320X240,5.7寸;

☆SD卡单元:

通信频率最高25MHz,芯片W86L388D,兼容MMC卡;

☆键盘单元:

4X4键盘,带8位LED数码管;芯片HD7279A;

☆模拟输入输出单元:

8个带自锁的按键,及8个LED发光管;

☆A/D转换单元:

芯片自带的8路10位A/D,满量程2.5V;

☆信号源单元:

方波输出;

☆标准键盘及PS2鼠标接口;

☆标准的IDE硬盘接口;

☆达盛公司的Tech_V总线接口;

☆达盛公司的E_Lab总线接口;

☆调试接口:

20针JTAG;

☆CPLD单元;

☆电源模块单元。

1.2核心板的资源介绍

1.核心板的硬件资源(ARM920T核)

在核心CPU板上包括下列单元和芯片,32位ARM920T的处理器,即三星的S3C2410芯片,两片动态存储器,每片32M字节,一片32M字节的NAND_flash存储器,一个USB主接口,一个USB从接口,一个10/100M的以太网控制芯片,完成网络访问功能,一个UART接口,完成串口通信,最高波特率率为115200bps,一个RTC实时时钟,一个5V转3.3V和1.8V的电源管理模块,一个20针的JTAG调试接口。

具体元器件见表1-1。

芯片名称

数量

功能

板上标号

S3C2410

1

ARM920T,中央处理器

S3C2410X

HY57V561620

2

动态存储器(SDRAM),32MB/片

HY57V561620

K9F5608

1

海量存储器,32MB

K9F5608U

AX88796

1

10/100M以太网控制器

AX88796

AS1117-3.3

1

5V转3.3V

AS1117-3.3

AS1117-1.8

1

5V转1.8V

AS1117-1.8

MAX3232

1

RS232转换

IMP811-S

1

复位

IMP811

表1-1

具体的单元、跳线见表1-2。

标号

名称

功能

JP1

JTAG复位单元

控制nRESET与nTRST是否接通

AREFSEL

模拟参考电压选择

短接后连接到VDD33,否则接地

3S/4S

3Step与4Step选择

设置NandFlash的运行模式,选择NCON(CPU引脚)与3Step、4Step连接

RESET

复位键

系统复位按键

P.S

电源插座

电源插座,接5V电源

SW

电源开关

拨向EXT接通,拨向INT断开电源

USB-HOST

主USB单元

主USB

UART0(CROSS/F)

串口0单元

和S3C2410的串口0通信

USB-DEVICE

从USB单元

USB设备

RJ45

网络单元

访问以太网

ARM-JTAG

JTAG插座

20针JTAG插座,用于与宿主机通信

INTERFACEC

功能单元

INTERFACEB

数据、地址单元

INTERFACEA

功能单元

表1-2

表1-3为核心板上各LED指示灯的意义。

标号

名称

功能

PWR

LED灯

电源指示灯

LED1

LED灯

GPI/O口G口的第8位指示

LED2

LED灯

GPI/O口G口的第9位指示

表1-3

表1-4为核心板上的晶振单元

标号

名称

功能

12MHz

CPU主时钟晶振

外接12MHz

32KHz

RTC时钟晶振

外接32.768KHz

25MHz

网络时钟晶振

外接25MHz

表1-4

2.核心板资源的具体介绍

1)电源模块

在S3C2410CPU板上由于其内核采用1.8V,I/O接口采用3.3V供电,因此需要将通用的5V转换成1.8V和3.3V。

图1-1-2为使用LM1117电源转换芯片把5V转成3.3V和1.8V的转换电路。

图1-1-2

2)NAND_FLASH海量存储器单元

该存储单元在板卡上标号为K9F5608U,选用32MB字节的K9F5608U,8位数据总线,该芯片由S3C2410的相关引脚直接控制,CPU分配给它的地址空间为0x00000000—0x01ffffff。

启动代码部分则放在从0x00000000开始的地址空间内。

系统将CPU的引脚OM[1:

0]设置成00b,当核心板上电复位时,系统首先将Nand_Flash开始的0~4K的程序映射到SteppingStone区,然后从那里开始执行。

Nand_Flash可以存放数据和程序,但需要特定的指令进行读写。

3)同步动态存储器单元

该存储单元在板卡上标号为HY57V561620。

选用两片8MB字节的HY57V561620,32位数据总线。

片选NSCS6接两片HY57V561620单元作为片选信号,CPU分配给这两片HY57V561620单元的地址空间分别为0x30000000-0x31ffffff,0x32000000-0x33ffffff,也就是S3C2410CPU的Bank6区和Bank7区。

4)RS232串口单元

该存储单元在板卡上标号为UART0(CROSS/F),选用了MAX3232电压转换芯片,进行PC机与CPU板的串口通讯。

它采用收、发、地,三线连接,无握手信号。

通过S3C2410内部的串口0控制器进行控制。

5)主/从USB单元

该单元在板卡上标号为USB-HOST和USB-DEVICE,通过S3C2410内部的USB主控制器和USB设备控制器进行控制。

6)网络单元

该存储单元在板卡上标号为AX88796,选用了ASIX公司的AX88796网络芯片,传输速率为10/100M自适应,16位数据总线传输,片选NGCS2接网络单元。

CPU分配给AX88796单元的地址空间为0x10000000—0x18000000,也就是S3C2410CPU的bank2区。

S3C2410CPU的外部中断ExINT2响应该中断。

RJ45插座上面自带数据传输的指示灯。

为清楚显示核心板上各存储区及单元,见表1-5。

标号

名称

存储区

存储的有效区

容量(字节)

HY57V561620

同步动态存储器

Bank7

0x32000000-0x33ffffff

32M

HY57V561620

同步动态存储器

Bank6

0x30000000-0x31ffffff

32M

AX88796

网络控制器

Band2

0x10000000后的若干

若干寄存器

NAND_FLASH

海量存储器

Bank0

0x00000000-0x01ffffff

32M

表1-5

7)JTAG单元

JTAG(JointTestActionGroup,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(TestAccessPort,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。

标准的JTAG接口是4线:

TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。

目前JTAG接口的连接有两种标准,即14针接口和20针接口,EL-ARM-830核心板上使用的是20针接口。

接口定义见表1-6。

引脚

名称

描述

1

VTref

目标板参考电压,接电源

2

VCC

接电源

3

nTRST

测试系统复位信号

4、6、8、10、12、

14、16、18、20

GND

接地

5

TDI

测试数据串行输入

7

TMS

测试模式选择

9

TCK

测试时钟

11

RTCK

测试时钟返回信号

13

TDO

测试数据串行输出

15

nRESET

目标系统复位信号

17、19

NC

未连接

表1-6

在核心板上,JTAG的第1脚用一黄色的方框标注,当串口、USB口、网络口向左摆放时,第1脚下面的管脚为第2脚,它左面的管脚依次为3,5,…,19;第2脚左面的管脚依次为4,6,…,20。

8)核心CPU板上的外接接口单元

在CPU板上有INTERFACEA、INTERFACEB、INTERFACEC,3个外扩接口单元,现对这三个接口的引脚加以说明。

INTERFACEB:

INTERFACEB扩展信号是地址、数据总线和读写、片选信号:

见表1-7

序号

代号

含义

IO

备注

1

+5V

+5V电源

2

+5V

+5V电源

3

LA19

地址线

O

4

LA18

地址线

O

5

LA17

地址线

O

6

LA16

地址线

O

7

EXA15

地址线

O

8

EXA14

地址线

O

9

EXA13

地址线

O

10

EXA12

地址线

O

11

GND

地

12

GND

地

13

EXA11

地址线

O

14

EXA10

地址线

O

序号

代号

含义

IO

备注

15

EXA9

地址线

O

16

EXA8

地址线

O

17

EXA7

地址线

O

18

EXA6

地址线

O

19

EXA5

地址线

O

20

EXA4

地址线

O

21

+5V

+5V电源

22

+5V

+5V电源

23

EXA3

地址线

O

24

EXA2

地址线

O

25

EXA1

地址线

O

26

EXA0

地址线

O

27

LA21

地址线

O

28

LA20

地址线

O

29

NC

空脚

30

NC

空脚

uedit

31

GND

地

32

GND

地

33

NC

空脚

空

34

NC

空脚

空

35

NC

空脚

空

36

NC

空脚

空

37

NC

空脚

空

38

NC

空脚

空

39

NC

空脚

空

40

NC

空脚

空

41

VDD33

+3.3V电源

42

VDD33

+3.3V电源

43

NC

空脚

空

44

NC

空脚

空

45

NC

空脚

空

46

NC

空脚

空

47

NC

空脚

空

48

NC

空脚

空

49

NC

空脚

空

50

NC

空脚

空

序号

代号

含义

IO

备注

51

GND

地

52

GND

地

53

EXD15

数据线

IO

54

EXD14

数据线

IO

55

EXD13

数据线

IO

56

EXD12

数据线

IO

57

EXD11

数据线

IO

58

EXD10

数据线

IO

59

EXD9

数据线

IO

60

EXD8

数据线

IO

61

GND

地

62

GND

地

63

EXD7

数据线

IO

64

EXD6

数据线

IO

65

EXD5

数据线

IO

66

EXD4

数据线

IO

67

EXD3

数据线

IO

68

EXD2

数据线

IO

69

EXD1

数据线

IO

70

EXD0

数据线

IO

71

GND

地

72

GND

地

73

LNOE

使能信号

O

74

LNWE

写信号

O

75

LNOE

使能信号

O

76

NWIT

等待信号

I

77

NC

空脚

空

78

NGCS0

片选信号

O

79

GND

地

80

GND

地

表1-7

INTERFACEA:

INTERFACEA扩展信号外设信号接口:

见表1-8。

序号

代号

含义

IO

备注

1

+12V

+12V电源

2

-12V

-12V电源

3

GND

地

序号

代号

含义

IO

备注

4

GND

地

5

+5V

+5V电源

6

+5V

+5V电源

7

GND

地

8

GND

地

9

+5V

+5V电源

10

+5V

+5V电源

11

NC

空脚

空

12

NC

空脚

空

13

NC

空脚

空

14

NC

空脚

空

15

NC

空脚

空

16

NC

空脚

空

17

NC

空脚

空

18

NC

空脚

空

19

+3.3V

+3.3V电源

20

+3.3V

+3.3V电源

21

SPICLK0

SPI时钟输出

O

CPU引脚

22

MISO0

SPI数据输入

I

CPU引脚

23

nSS0

SPI片选

O

CPU引脚

24

MOSI0

SPI数据输出

O

CPU引脚

25

GND

地

26

GND

地

27

NC

空脚

空

28

NC

空脚

空

29

NC

空脚

空

30

NC

空脚

空

31

GND

地

32

GND

地

33

NC

空脚

空

34

NC

空脚

空

35

IISLRCLK

IIS左右声道时钟

O

36

IISDO

IIS数据输出

O

37

GND

地

38

GND

地

序号

代号

含义

IO

备注

39

IISCLK

IIS输出时钟

O

40

NC

空脚

空

41

NC

空脚

空

42

IISDI

IIS数据输入

I

43

GND

地

44

GND

地

45

TOUT0

定时器输出0

O

46

TCLK0

定时器时钟输出0

连接至CPU的TCLK0引脚

47

NC

空脚

空

48

EINT1

中断1

I

外部输入的中断信号,连接到CPU的中断

49

TOUT1

定时器输出1

50

TCLK1

定时器时钟输出1

连接至CPU的TCLK1引脚

51

GND

地

52

GND

地

53

EINT0

中断0

I

外部输入的中断信号,连接到CPU的中断

54

NC

空脚

空

55

NC

空脚

空

56

NGCS1

片选信号1

O

57

NC

空脚

空

58

NC

空脚

空

59

RESET

复位信号

O

60

NC

空脚

空

61

GND

地

62

GND

地

63

NC

空脚

空

64

NC

空脚

空

65

NC

空脚

空

66

NC

空脚

空

67

EINT7

中断7

I

外部输入的中断信号,连接到CPU的中断

68

EINT3

中断3

I

外部输入的中断信号,连接到CPU的中断

69

NGCS3

片选信号3

O

序号

代号

含义

IO

备注

70

NGCS1

片选信号1

O

71

NC

空脚

空

72

NC

空脚

空

73

NC

空脚

空

74

NC

空脚

空

75

NC

空脚

空

76

GND

地

77

GND

地

78

NC

空脚

空

79

GND

地

80

GND

地

表1-8

INTERFACEC用来扩展INTERFACEA、INTERFACEB没有扩展的CPU信号,如AD输入、液晶、串口等和扩展子板间的通讯信号。

见表1-9。

序号

代号

含义

IO

备注

1

+5V

+5V电源

2

+5V

+5V电源

3

AIN0

模拟输入0

I

4

AIN1

模拟输入1

I

5

AIN2

模拟输入2

I

6

AIN3

模拟输入3

I

7

AIN4

模拟输入4

I

8

AIN5

模拟输入5

I

9

AREFB

模拟输入负参考电压

I

10

AREFT

模拟输入正参考电压

I

11

AVCOM

模拟输入参考电压公共端

I

12

TOUT2

定时器输出2

O

13

TOUT3

定时器输出3

O

14

NC

空脚

15

ExINT4

外部中断4

I

16

ExINT5

外部中断5

I

17

ExINT6

外部中断6

I

18

ExINT7

外部中断7

I

19

nGCS4

片选

O

20

nGCS5

片选

O

序号

代号

含义

IO

备注

21

NGCS4

片选

O

22

nGCS5

片选

O

23

LnWBE0

写字节使能0

O

24

LnWBE1

写字节使能1

O

25

LnWBE2

写字节使能2

O

26

LnWBE3

写字节使能3

O

27

UCLK

输入输出口

IO

28

GPH1

输入输出口

IO

29

CLKOUT0

时钟输出信号源0

O

30

CLKOUT1

时钟输出信号源1

O

31

IICSCL

IIC总线时钟

O

32

IICSDA

IIC总线数据

IO

33

RXD1

串口1接收数据

I

34

TXD1

串口1发送数据

O

35

RXD2

串口2接收数据

I

36

TXD2

串口2发送数据

O

37

SDDAT0

SD卡数据0

O

EL-830底板未使用

38

SDDAT1

SD卡数据1

O

EL-830底板未使用

39

SDDAT2

SD卡数据2

O

EL-830底板未使用

40

SDDAT3

SD卡数据3

O

EL-830底板未使用

41

SDCLK

SD卡时钟

O

EL-830底板未使用

42

SDCMD

SD卡命令

O

EL-830底板未使用

43

AIN6

模拟输入6

I

44

AIN7

模拟输入7

I

45

NC

空脚

46

CDCLK

CPU信号,解码器系统时钟

O

47

VD19

液晶数据19

O

CPU引脚

48

VD20

液晶数据20

O

CPU引脚

49

VD21

液晶数据21

O

CPU引脚

50

VD22

液晶数据22

O

CPU引脚

51

VD23

液晶数据23

O

CPU引脚

52

VD10

液晶数据10

O

CPU引脚

53

VD11

液晶数据11

O

CPU引脚

54

VD12

液晶数据12

O

CPU引脚

55

VD13

液晶数据13

O

CPU引脚

序号

代号

含义

IO

备注

56

VD14

液晶数据14

O

CPU引脚

57

VD15

液晶数据15

O

CPU引脚

58

VD3

液晶数据3

O

CPU引脚

59

VD4

液晶数据4

O

CPU引脚

60

VD5

液晶数据5

O

CPU引脚

61

VD6

液晶数据6

O

CPU引脚

62

VD7

液晶数据7

O

CPU引脚

63

TSMX

接触摸屏XN脚

O

CPU引脚

64

TSMY

接触摸屏YN脚

O

CPU引脚

65

TSPY

接触摸屏YP脚

O

CPU引脚

66

TSPX

接触摸屏XP脚

O

CPU引脚

67

VM-VDEN

液晶电压控制信号

I

68

VF-VS

液晶桢时钟

O

69

VL-HS

液晶线时钟

O

70

VCLK

液晶位时钟

O

71

VD0

液晶数据0

O

72

VD1

液晶数据1

O

73

VD2

液晶数据2

O

74

VD3

液晶数据3

O

75

VD4

液晶数据4

O

76

VD5

液晶数据5

O

77

VD6

液晶数据6

O

78

VD7

液晶数据7

O

79

GND

地

80

GND

地

表1-9

1.3实验箱底板的资源介绍

1.概述

实验箱底板上的资源丰富,具

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 嵌入式 设计 论文 参考 ARM 实验 指导书

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx