软件总体架构图1.docx

软件总体架构图1.docx

- 文档编号:10346112

- 上传时间:2023-02-10

- 格式:DOCX

- 页数:18

- 大小:217.08KB

软件总体架构图1.docx

《软件总体架构图1.docx》由会员分享,可在线阅读,更多相关《软件总体架构图1.docx(18页珍藏版)》请在冰豆网上搜索。

软件总体架构图1

1软件总体架构图

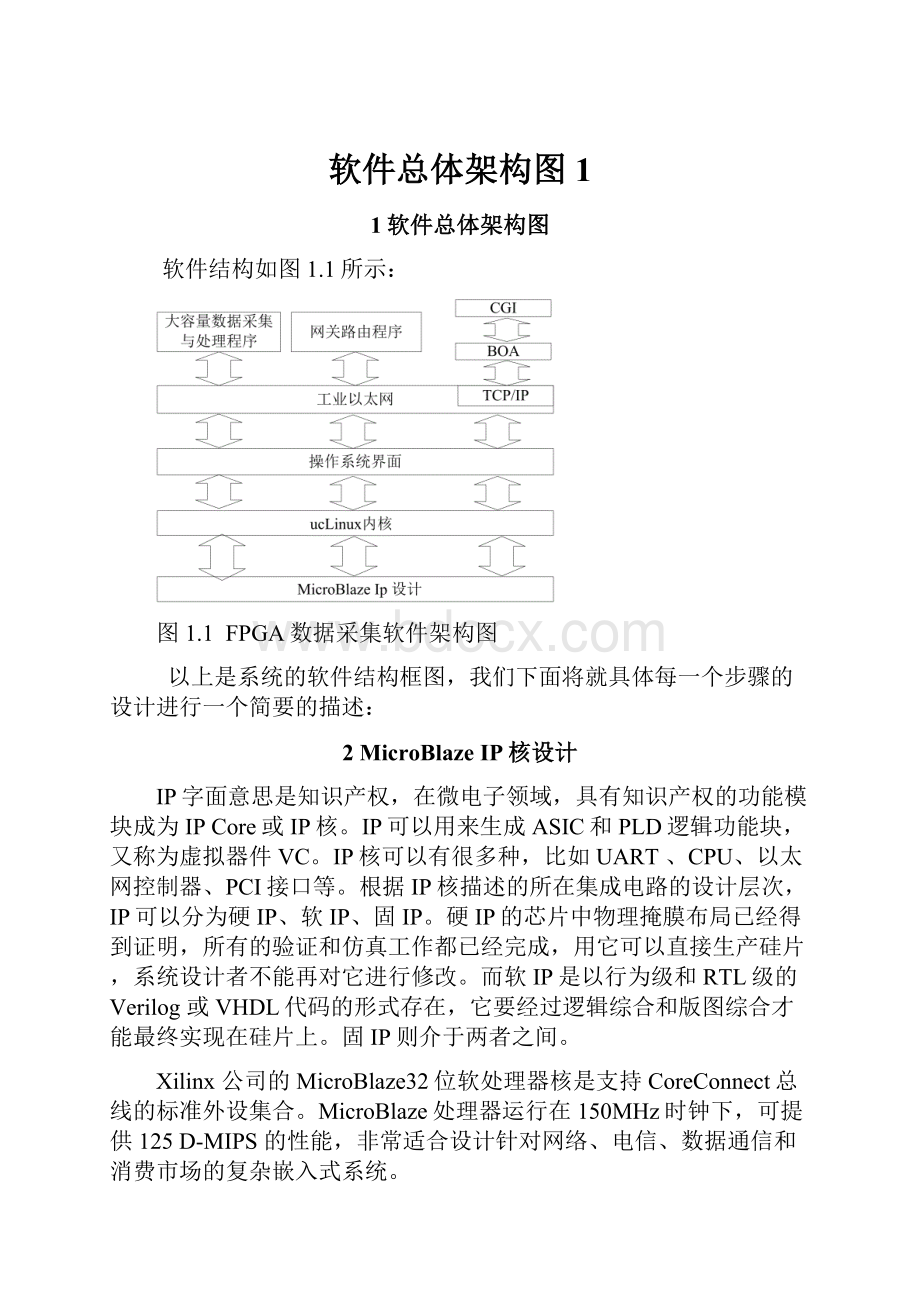

软件结构如图1.1所示:

图1.1FPGA数据采集软件架构图

以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:

2MicroBlazeIP核设计

IP字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IPCore或IP核。

IP可以用来生成ASIC和PLD逻辑功能块,又称为虚拟器件VC。

IP核可以有很多种,比如UART、CPU、以太网控制器、PCI接口等。

根据IP核描述的所在集成电路的设计层次,IP可以分为硬IP、软IP、固IP。

硬IP的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP是以行为级和RTL级的Verilog或VHDL代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP则介于两者之间。

Xilinx公司的MicroBlaze32位软处理器核是支持CoreConnect总线的标准外设集合。

MicroBlaze处理器运行在150MHz时钟下,可提供125D-MIPS的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze的体系结构

MicroBlaze是基于Xilinx公司FPGA的微处理器IP核,和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze处理器采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其中的数据,如图4.1所示

图2.1MicroBlaze内核结构框图

(1)内部结构

MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器——PC指针和MSR状态标志寄存器。

为了提高性能,MicroBlaze还具有指令和数据缓存。

所有的指令字长都是32位,有3个操作数和2种寻址模式。

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。

指令执行的流水线是并行流水线,它分为3级流水:

取指、译码和执行,如图4.2所示。

图2.2MicroBlaze的流水线

(2)存储结构

MicroBlaze是一种大端存储系统处理器,使用如图4.3所式的格式来访问存储器。

图2.3大端数据格式

(3)中断控制和调试接口

MicroBlaze可以响应软件和硬件中断,进行异常处理,通过外加控制逻辑,可以扩展外部中断。

利用微处理器调试模块(MDM)IP核,可通过JTAG接口来调试处理器系统。

多个MicroBlaze处理器可以用1个MDM来完成多处理器调试。

(4)快速单一链路接口

MicroBlaze处理器具有8个输入和8个输出快速单一链路接口(FSL)。

FSL通道是专用于单一方向的点到点的数据流传输口。

FLS和MicroBlaze的接口宽度是32位。

每一个FSL通道都可以发送和接收控制或数据字。

2.CoreConnect技术

CoreConnect是由IBM开发的片上总线通信链,它使多个芯片核相互连接成为一个完整的新芯片成为可能。

CoreConnect技术使整合变得更为容易,而且在标准产品平台设计中,处理器、系统以及外围的核可以重复使用,以达到更高的整体系统性能。

Xilinx将为所有嵌入式处理器用户提供IBMCoreConnect许可,因为它是所有Xilinx嵌入式处理器设计的基础。

MicroBlaze处理器使用了与IBMPowerPC相同的总线,用作外设。

虽然MicroBlaze软处理器完全独立于PowerPC,但它让设计者可以选择芯片上的运行方式,包括一个嵌入式PowerPC,并共享它的外设。

CoreConnect总线架构如图4.4所示。

它包括片上外围总线(OPB),处理器本机总线(PLB),设备控制寄存器(DCR)总线以及1个总线桥和2个判优器。

图2.4CoreConnect总线架构

(1)片上外设总线(OPB)

内核通过片上外设总线(OPB)来访问低速和低性能的系统资源。

OPB是一种完全同步总线,它的功能处于一个单独的总线层级。

它不是直接连接到处理器内核的。

OPB接口提供分离的32位地址总线和32位数据总线。

处理器内核可以借助“PLBtoOPB”桥,通过OPB访问从外设。

作为OPB总线控制器的外设可以借助“OPBtoPLB”桥,通过PLB访问存储器。

(2)处理器本机总线(PLB)

PLB接口为指令和数据一侧提供独立的32位地址和64位数据总线。

PLB支持具有PLB总线接口的主机和从机通过PLB信号连接来进行读写数据的传输。

总线架构支持多主从设备。

每一个PLB主机通过独立的地址总线、读数据总线和写数据总线与PLB连接。

PLB从机通过共享但分离的地址总线、读数据总线和写数据总线与PLB连接,对于每一个数据总线都有一个复杂的传输控制和状态信号。

为了允许主机通过竞争来获得总线的所有权,有一个中央判决机构来授权对PLB的访问。

(3)设备控制寄存器总线(DCR)

设备控制寄存器总线(DCR)是为在CPU通用寄存器(GPRs)和DCR的从逻辑设备控制寄存器(DCRs)之间传输数据而设计的。

3.MicroBlaze的开发

应用EDK(嵌入式开发套件)可以进行MicroBlazeIP核的开发。

工具包中集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。

EDK中提供一个集成开发环境XPS(XilinxPlatformStudio),以便使用系统提供的所有工具,完成嵌入式系统开发的整个流程。

EDK中还带有一些外设接口的IP核,如LMB、OPB总线接口、外部存储控制器、SDRAM控制器、UART、中断控制器、定时器等。

利用这些资源,可以构建一个较为完善的嵌入式微处理器系统。

在FPGA上设计的嵌入式系统层次结构为5级,可在最低层硬件资源上开发IP核,或利用已开发的IP核搭建嵌入式系统,这是硬件开发部分;开发IP核的设备驱动、应用接口(API)和应用层(算法),属软件开发内容。

利用MicroBlaze构建基本的嵌入式系统如图4.5所示。

通过标准总线接口——LMB总线和OPB总线的IP核,MicroBlaze就可以和各种外设IP核相连。

图2.5MicroBlaze系统架构图

EDK中提供的IP核均有相应的设备驱动和应用接口,使用者只需利用相应的函数库,就可以编写自己的应用软件和算法程序。

对于用户自己开发的IP核,需要自己编写相应的驱动和接口函数。

软件设计流程如图4.6所示。

图2.6软件开发流程

3移植uclinux

首先不管什么平台,移植uclinux,整个流程都遵从于:

Kernelpreparation—>isntallBSP—>Buildhardwareplatform—>Memorytest—>Buildkernelimage—>Download具体来说,如下图4.7所示:

图3.1uclinux移植流程

1.搭建开发环境

操作系统:

RedhatHatLinux9,安装的时候添加开发和编译环境。

(编译内核)Windows(安装EDK)

交叉编译工具:

针对不同的CPU系列,有不同的编译环境,通常,程序是在一台计算机上编译,然后再分布到将要使用的其他计算机上。

当主机系统(运行编译器的系统)和目标系统(产生的程序将在其上运行的系统)不兼容时,该过程就叫做交叉编译。

建立一个交叉编译工具链是一个相当复杂的过程,网上有一些编译好的可用的交叉编译工具链可以下载。

下载并安装好,我们的编译环境就搭建好了。

(1)下载并创建BSP

从petalogix站点下载BSP,并安装到电脑上。

把在EDK下生成的包含硬件系统信息的“auto-config.in”文件复制到linux的/home/devel/src\uClinux-2.4.x\arch\microblaze\platform\uclinux-auto路径下。

编译器需要从auto-config.in文件里知道“theaddressmapandtheprocessorsystem”以及其它相关信息。

(2)配置内核

在网站上下载源代码包,并安装在系统的任意目录。

此时,就可以使用命令来进行内核的配置了:

$cd~/uClinux-dist

$makemenuconfig

这里,我们需要进行一系列内核配置的选择。

(3)编译内核生成image文件

$cd~/uClinux-dist

$makedep

$makeclean

$make

这个过程期间将完成下面的内容:

编译内核(Buildkernel)

编译uclinux的C库(Clibraries)

编译用户程序(userapplications)

转换成二进制文件

编译内核文件系统

合并内核和文件系统为一个二进制文件

编译成功,你就会在uClinux-dist的目录下发现一个新的目录images。

里面就包含了你编译成功的系统文件,image.elf和image.bin两个文件。

(4)下载内核文件到目标板

将在上面编译生成的内核文件image.bin下载到目标板上去并运行.

4.1移植工业以太网协议

由于Spartan-3E只提供了物理层(PHY)的网络控制器,所以对于处理本装置的物理层以上的网络设备,需要重新制定适合本系统的网络协议。

工业以太网EtherNet/IP,是一种适用于工业环境的通讯体系,能够在广阔的区域中支持大量现场设备的连接。

它采用通用工业协议(CIP)作为其应用层协议。

CIP协议支持各种控制、配置和信息处理服务,包括显式报文(用于信息传输,灵活的报文交换)以及隐式报文(用于控制和实时I/O数据的传输),支持轮询、周期和状态改变数据传输触发机制,点对点单播和广播数据传输方式[3]。

OE服务的设计简化了EtherNet/IP的移植,只需要修改操作环境文件来适合FPGA操作体系。

4.2移植BOA

从www.boa.org下载一个主流版本的BOA源码包,本系统用的是boa-0.94.13.tar.gz。

第一步:

修改Makefile文件,编译BOA源码,生成BOA可执行文件。

修改Makefile文件,因为我们要编译的是二进制代码,所以必须修改Makefile中的CC和CPP,然后运行make进行编译,得到可执行程序BOA。

第二步:

配置BOA。

BOA启动时将加载一个配置文件boa.conf,在boa程序运行前,必须首先编辑该文件。

在Boa源码目录下已有一个示例boa.conf,可以在其基础上修改。

配置好的主要内容如下:

Usernobody

Group0

ServerNameXilinxFPGA

ErrorLog/var/log/boa/error_log

AccessLog/var/log/boa/access_log

DocumentRoot/var/www

MimeTypes/etc/mime.types

ScriptAlias/cgi-bin//var/www/cgi-bin/

据此配置,需要创建日志文件目录/var/log/boa,HTML文档的主目录/var/www,将静态网页存入该目录下,CGI脚本所在目录/var/www/cgi-bin,将cgi的脚本存放在该目录下。

4.3CGI网关接口程序

CGI(通用网关接口)提供Web服务器一个执行外部程序的通道,这种服务端技术建立了Web浏览器与Web服务器之间的交互。

首先,浏览器将远程客户端发送的请求送到Web服务器,Web服务器将数据使用STDIN送给CGI程序,执行CGI程序后获得缓冲区中的设备信息,最后,使用STDOUT输出包含工业设备信息的HTML形式的结构文件,经Web服务器送回浏览器,显示给远程客户端。

CGI程序可以用C语言编写,并且能够嵌入HTML脚本。

经过编译器编译以后,CGI程序可以使用GET、POST或直接的URL参数传递方法与远程客户端通信。

以下是将采集到的设备数据显示到网页上的一段CGI程序,其中用到的数据库是SQLite。

SQLite是用一个小型C库实现的一种强有力的嵌入式关系数据库管理体制,它在体积与功能之间做到了较好的平衡,是理想的嵌入式数据库。

#include

#include"sqlite3.h"

main(){

…

sqlite3*p_db;

sqlite3_open("mydb",&p_db);/*打开数据库*/

/*执行SQL语句选择alarm表中的所有记录,并在查询结果的每一行上执行回调函*/

ret=sqlite3_exec(p_db,"select*fromalarm;",callback,0,&errmsg);

…

sqlite3_close(p_db);/*关闭数据库*/

}

intcallback(void*p_data,intn_columns,char**column_names,char**column_values){/*回调函数*/

inti;

for(i=0;i printf("%s=%s\n",column_names[i],column_values[i]? column_values[i]: "NULL");/*打印出查询结果*/ return0; } 4.4动态网页技术 通过后期的软件设计和界面设计,实现服务器端和客户端间的通信的B/S结构,用户不需要在客户机一端安装数据检测的客户端即可以在远程进行设备的数据采集并进行故障的诊断,从而形成一个开放式的远程监测与故障诊断系统。 系统动态页面效果如图3.4所示: 图4.1系统动态页面效果图 5MicroBlazeuClinuxNetworking uClinux最突出的一个地方就是它配套的网络协议以及工具。 这里我们说明怎样将TCP/IP协议配置起来,并让它在我们的目标板上运行起来。 (1)准备工作: 1.确定uClinux源码包是最新版本,并且与uClinuxCVS合成。 2.下载并使用了必要的补丁。 3.确定使用最新的gcctoolchain。 (2)内核配置: 在uClinux-dist文件夹下运行“makemenuconfig”,并按照下面的示意选择: TargetPlatformSelection [*]CustomizeKernelSettings Processortypeandfeatures [*]Ethernetdriver GeneralSetup [*]Networkingsupport NetworkingOptions [*]Unixdomainsockets [*]TCP/IPnetworking 如果需要NFS支持,还要做如下选择: Filesystems NetworkFileSystems [*]NFSfilesystemsupport [*]ProvideNFSv3clientsupport 保存并退出. 如果需要修改Xilinx目标板的网络MAC地址,可以修改项目中的system.mh文件,并编辑uClinux-dist/linux-2.4.x/include/asm-MicroBlaze/xparamet- ers.h文件中相应项。 (3)服务配置: 仍然是在uClinux-dist文件夹下运行“makemenuconfig”,按如下示意选择。 这些不是必选的,是否选择取决于你想使用哪种应用。 最低标准,应该选择ping,inetd和telnetd三种服务,这可以实现最基本的TCP/IP网络功能。 [*]CustomizeVendor/UserSettings NetworkApplications [*]inetd [*]ping [*]portmap(如果需要NFS服务则选中) [*]telnetd Busybox [*]ifconfig [*]ifconfig: statusreporting [*]ifconfig: enablehwoption [*]ifconfig: extraoptions [*]mount [*]mount: loopdevices [*]mount: supportNFSmounts(如果需要NFS服务则选中) [*]telnet(非必选) [*]tftp [*]tftp: put [*]tftp: get 保存并退出. 最后,依次运行 makedep makeclean make 来编译我们新完成的配置,生成映像文件。 测试: 编译完成后,新的映像image.bin和image.elf应该在uClinux-dist/images文件夹中。 使用xmd,将映像下载到目标板中并运行内核。 当内核启动完成,在命令行提示符输入以下命令: />hostnameMicroBlaze1 (这是给主机起名字,它可以是任何合乎规则的名字,这里是MicroBlaze1) />ifconfiglo127.0.0.1 />ifconfigeth0xx.xx.xx.xxnetmaskxx.xx.xx.xxbroadcastxx.xx.xx.xx 确定IP地址以及子网掩码地址,广播地址。 然后,可以尝试自己ping自己(按Ctrl+C退出): />ping127.0.0.1 PING127.0.0.1(127.0.0.1): 56databytes 64bytesfrom127.0.0.1: icmp_seq=0ttl=64time=0.0ms 64bytesfrom127.0.0.1: icmp_seq=1ttl=64time=10.0ms 64bytesfrom127.0.0.1: icmp_seq=2ttl=64time=10.0ms 64bytesfrom127.0.0.1: icmp_seq=3ttl=64time=10.0ms ^C ---127.0.0.1pingstatistics--- 5packetstransmitted,5packetsreceived,0%packetloss round-tripmin/avg/max=0.0/8.0/10.0ms 可以试着ping局域网中另外一台机器(这里ping地址192.168.0.41) />ping192.168.0..41 PING192.168.0.41(192.168.0.41): 56databytes 64bytesfrom192.168.0.41: icmp_seq=0ttl=64time=10.0ms 64bytesfrom192.168.0.41: icmp_seq=1ttl=64time=0.0ms 64bytesfrom192.168.0.41: icmp_seq=2ttl=64time=0.0ms 64bytesfrom192.168.0.41: icmp_seq=3ttl=64time=0.0ms 64bytesfrom192.168.0.41: icmp_seq=4ttl=64time=0.0ms ^C ---192.168.0.41pingstatistics--- 5packetstransmitted,5packetsreceived,0%packetloss round-tripmin/avg/max=0.0/2.0/10.0ms 最后,从网络中另外一台机器远程登录MicroBlaze(使用上面ifconfig命令中分配的IP地址) [root@zxt]$telnetMicroBlaze1 Trying192.168.0.34... ConnectedtoMicroBlaze1. Escapecharacteris'^]'. MicroBlaze1login: root Nodirectory,logginginwithHOME=/ Welcome onMicroBlaze. Sashcommandshell(version1.1.1) /> 6ADC数据采集 当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此,随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便得到更宽的频率搜索范围,获取更多的信息量。 因此,通信系统对信号处理前端的A/D采样电路提出了更高的要求,即希望A/D转换速度快而采样精度高,以便满足系统处理的要求。 可编程门阵列FPGA的出现已经显著改变了数字系统的设计方式。 应用可编程门阵列FPGA,可使数字系统设计具有高度的灵活性,因此FPGA的应用越来越广泛,Spartan-3EFPGA系列,是赛灵思公司推出的采用先进90nm制造工艺技术生产的系列产品,其自带的双通道AD数模转换控制器,可以方便的实现数据的采集,配上LTC6912-1的双通道放大器,可以使得收集数据的精确性达到mV级。 1.高速采集系统介绍 数据采集系统原理框图如图1所示,输入的中频信号经A/D采样电路采样后,通过信号放大器,将收集到的信号,调整成为最佳的检测信号,即1.65V±1.25V 输送到模拟转换器中,模拟信号转换器将收集的模拟信号,转换成为14-bit的数字信号。 其中,FPGA的作用是提供始终频率,并且控制放大和转换器的相互协调工作。 图6.1数据采集系统原理图 2.AMPSPI控制器 (1)LTC6912-1放大器的接口 图6.2LTC6912-1工作原理图 当AMP-CS输入是低电平的时候,LTC6912-1放大器开始工作。 在放大器的内部,有八个转换登记器(shiftregister),它们将产生一个增益的倍速信号,这样就可以按要求放大信号。 当AMP工作开始时,它会发送一个增益的倍速给FPGA,这个信号对于大多数应用来说是可以忽略的。 当AMP-CS重新回到高电平时,信号增益工作完成。 图6.3LTC6912-1内置转换登记器工作图 放大器内部的八个转换登记器,会为AGain和BGain产生两组编码,它们代表的意思如下: 其中,产生的Gain是增益的倍速,它的可能取值就只有7种情况。 Gain值的大小决定于输入电压的大小,不同的Gain值所能适应的电压福特数是不一样的,但整个来说,输入电压的范围是0.4-1.6625V 图6.4放大器转换编码值表 放大器的完整时序图如下: 图6.5放大器时序工作图 (2)LTC1407-1AD转换控制器 图6.6LTC1407-1A工作原理图 一个典型的信息传输需

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 软件 总体 架构

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx