太原理工大学EDA课设4位十进制计数显示器.docx

太原理工大学EDA课设4位十进制计数显示器.docx

- 文档编号:10218460

- 上传时间:2023-02-09

- 格式:DOCX

- 页数:13

- 大小:927.76KB

太原理工大学EDA课设4位十进制计数显示器.docx

《太原理工大学EDA课设4位十进制计数显示器.docx》由会员分享,可在线阅读,更多相关《太原理工大学EDA课设4位十进制计数显示器.docx(13页珍藏版)》请在冰豆网上搜索。

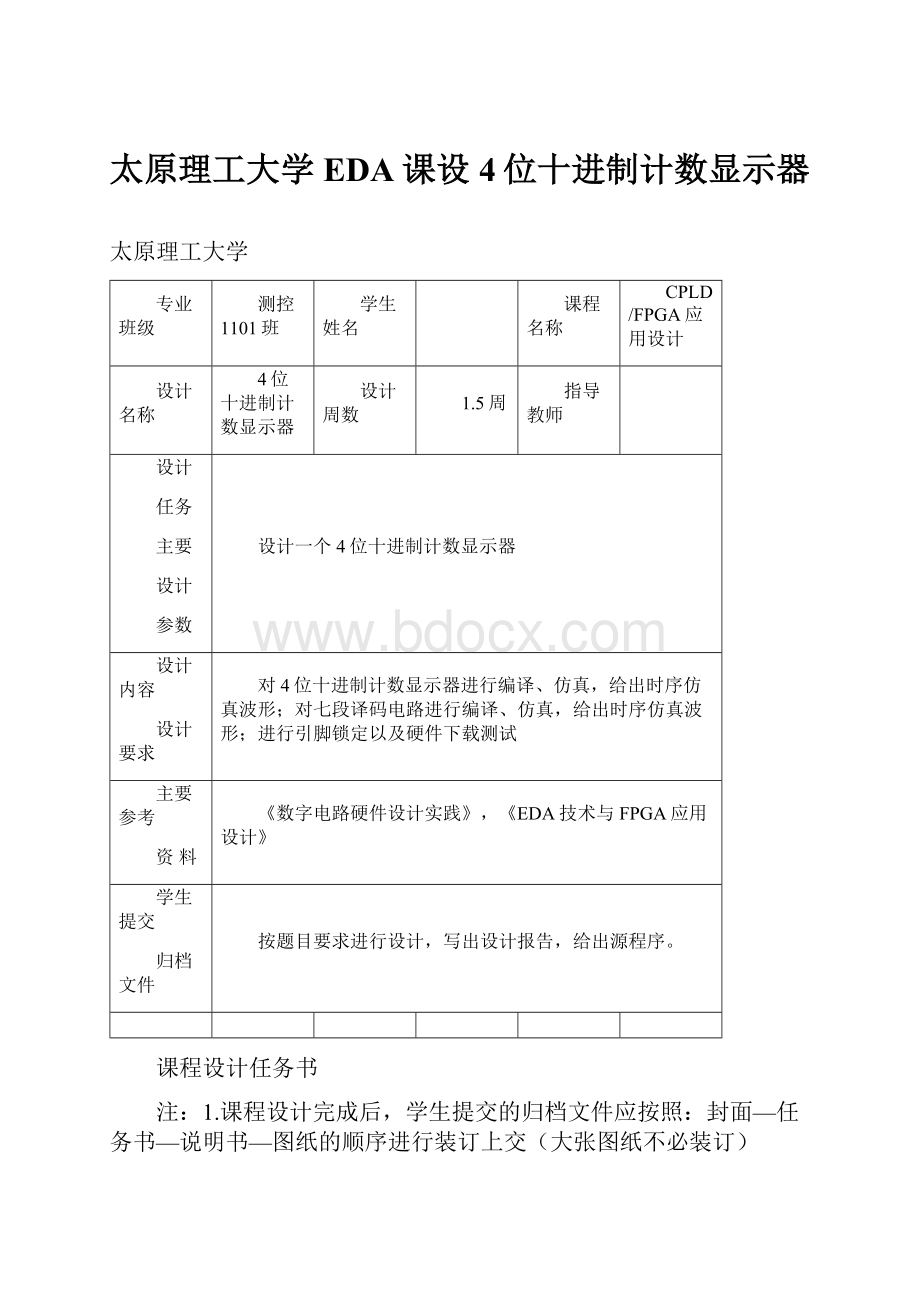

太原理工大学EDA课设4位十进制计数显示器

太原理工大学

专业班级

测控1101班

学生姓名

课程名称

CPLD/FPGA应用设计

设计名称

4位十进制计数显示器

设计周数

1.5周

指导教师

设计

任务

主要

设计

参数

设计一个4位十进制计数显示器

设计内容

设计要求

对4位十进制计数显示器进行编译、仿真,给出时序仿真波形;对七段译码电路进行编译、仿真,给出时序仿真波形;进行引脚锁定以及硬件下载测试

主要参考

资料

《数字电路硬件设计实践》,《EDA技术与FPGA应用设计》

学生提交

归档文件

按题目要求进行设计,写出设计报告,给出源程序。

课程设计任务书

注:

1.课程设计完成后,学生提交的归档文件应按照:

封面—任务书—说明书—图纸的顺序进行装订上交(大张图纸不必装订)

2.可根据实际内容需要续表,但应保持原格式不变。

指导教师签名:

日期:

目录

一、设计目的…………………………………………………………4

二、设计设备…………………………………………………………4

三、设计原理…………………………………………………………4

四、设计任务…………………………………………………………4

五、设计程序…………………………………………………………4

1、4位十进制计数电路……………………………………………………4

2、显示译码电路……………………………………………………………6

3、四选一数据选择器电路…………………………………………………7

4、2位二进制计数器电路…………………………………………………7

5、各电路连接的顶层文件设计……………………………………………8

六、对程序编译,仿真………………………………………………9

1、对4位十进制计数器的程序进行编译…………………………………9

2、对显示译码段编译、仿真………………………………………………10

3、对整体进行全局编译、引脚分配、波形仿真…………………………10

七、VHDL源文件下载到实验箱………………………………………12

八、设计总结…………………………………………………………13

设计一4位十进制计数显示器

一、设计目的

1.设计4位十进制计数器

2.设计输出低电平有效地七段显示译码器

3.显示计数器值

二、设计设备

EDA实验箱,计算机及QuartusⅡ软件。

三、设计原理

计数器是在数字系统中使用最多的时序电路,它不仅能用于对时钟脉冲计数,还可以用于分频,定时,产生节拍脉冲和脉冲序列以及进行数学运算等,计数器是一个典型的时序电路,分析计数器就能更好地了解时序电路的特性。

4位十进制计数器的设计分5步完成。

先设计4位十进制计数电路,之后设计显示译码电路,再设计四选一数据选择器电路,再设计2位二进制计数器,最后建立一个顶层文件将4者连接起来。

四、设计任务

(1)对四位十进制计数器进行编辑、编译、仿真。

(2)对七段译码电路进行编辑、编译、仿真。

(3)对四位十进制计数译码电路进行编辑、编译、仿真。

(4)进行引脚锁定以及硬件下载测试,记录实验结果。

五、设计程序

1.4位十进制计数电路

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCOU4IS

PORT(

CLK,RESET,CIN:

INSTD_LOGIC;

CO:

OUTSTD_LOGIC;

BCDAP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

BCDBP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

BCDCP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

BCDDP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

);

ENDCOU4;

ARCHITECTUREBEHAVEOFCOU4IS

SIGNALBCDAN:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALBCDBN:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALBCDCN:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALBCDDN:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

BCDAP<=BCDAN;

BCDBP<=BCDBN;

BCDCP<=BCDCN;

BCDDP<=BCDDN;

KK1:

PROCESS(CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

IF(RESET='0')THEN

BCDAN<="0000";

ELSIF(CIN='1')THEN

IF(BCDAN="1001")THEN

BCDAN<="0000";

ELSE

BCDAN<=BCDAN+'1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESSKK1;

KK2:

PROCESS(CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

IF(RESET='0')THEN

BCDBN<="0000";

ELSIF(CIN='1')AND(BCDAN="1001")THEN

IF(BCDBN="1001")THEN

BCDBN<="0000";

ELSE

BCDBN<=BCDBN+'1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESSKK2;

KK3:

PROCESS(CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

IF(RESET='0')THEN

BCDCN<="0000";

ELSIF(CIN='1')AND(BCDBN="1001")AND(BCDAN="1001")THEN

IF(BCDCN="1001")THEN

BCDCN<="0000";

ELSE

BCDCN<=BCDCN+'1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESSKK3;

KK4:

PROCESS(CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THEN

IF(RESET='0')THEN

BCDDN<="0000";

ELSIF(CIN='1')AND(BCDCN="1001")AND(BCDBN="1001")AND(BCDAN="1001")THEN

IF(BCDDN="1001")THEN

BCDDN<="0000";

ELSE

BCDDN<=BCDDN+'1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESSKK4;

ENDBEHAVE;

2.显示译码电路

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYSEG7IS

PORT(II:

INSTD_LOGIC_VECTOR(3DOWNTO0);

Y:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDSEG7;

ARCHITECTUREBEHAVEOFSEG7IS

SIGNALINDATA:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

INDATA<=II;

PROCESS(INDATA)

BEGIN

CASEINDATAIS

WHEN"0000"=>Y<="0111111";

WHEN"0001"=>Y<="0000110";

WHEN"0010"=>Y<="1011011";

WHEN"0011"=>Y<="1001111";

WHEN"0100"=>Y<="1100110";

WHEN"0101"=>Y<="1101101";

WHEN"0110"=>Y<="1111101";

WHEN"0111"=>Y<="0000111";

WHEN"1000"=>Y<="1111111";

WHEN"1001"=>Y<="1101111";

WHEN"1010"=>Y<="1110111";

WHEN"1011"=>Y<="1111100";

WHEN"1100"=>Y<="0111001";

WHEN"1101"=>Y<="1011110";

WHEN"1110"=>Y<="1111001";

WHEN"1111"=>Y<="1110001";

WHENOTHERS=>Y<="XXXXXXX";

ENDCASE;

ENDPROCESS;

ENDBEHAVE;

3.四选一数据选择器电路

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYmux4_1is

PORT(SEG1,SEG2,SEG3,SEG4:

INSTD_LOGIC_VECTOR(3downto0);

s:

INSTD_LOGIC_VECTOR(1DOWNTO0);

y:

OUTSTD_LOGIC_VECTOR(3downto0)

);

ENDmux4_1;

ARCHITECTUREBEHAVIORAL1OFmux4_1IS

BEGIN

PROCESS(SEG1,SEG2,SEG3,SEG4,s)

BEGINCASEsIS

WHEN"00"=>y<=SEG1;

WHEN"01"=>y<=SEG2;

WHEN"10"=>y<=SEG3;

WHEN"11"=>y<=SEG4;

WHENOTHERS=>y<="0000";

ENDCASE;

ENDPROCESS;

ENDBEHAVIORAL1;

4.2位二进制计数器电路

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcounter4is

PORT(CLK1:

INSTD_LOGIC;

CNT:

OUTSTD_LOGIC_VECTOR(1DOWNTO0)

);

ENDcounter4;

ARCHITECTUREBEHAVIORAL2ofcounter4IS

SIGNALcnt1:

STD_LOGIC_VECTOR(1DOWNTO0):

="00";

BEGIN

PROCESS(CLK1)

BEGIN

IFCLK1'EVENTANDCLK1='1'THEN

cnt1<=cnt1+1;

ENDIF;

ENDPROCESS;

CNT<=cnt1;

ENDBEHAVIORAL2;

5.各电路连接的顶层文件设计

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCOU47SEGIS

PORT(CLK,clk1,RESET,ENA:

INSTD_LOGIC;

SEG1:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

Sel:

outstd_logic_vector(1downto0));

ENDCOU47SEG;

ARCHITECTUREX47OFCOU47SEGIS

COMPONENTSEG7

PORT(II:

INSTD_LOGIC_VECTOR(3DOWNTO0);

Y:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDCOMPONENT;

COMPONENTCOU4

PORT(CLK,RESET,CIN:

INSTD_LOGIC;

BCDAP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

BCDBP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

BCDCP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

BCDDP:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

);

ENDCOMPONENT;

COMPONENTmux4_1

PORT(SEG1,SEG2,SEG3,SEG4:

INSTD_LOGIC_VECTOR(3downto0);

s:

INSTD_LOGIC_VECTOR(1DOWNTO0);

y:

OUTSTD_LOGIC_VECTOR(3downto0)

);

ENDCOMPONENT;

COMPONENTcounter4

PORT(CLK1:

INSTD_LOGIC;

CNT:

OUTSTD_LOGIC_VECTOR(1DOWNTO0)

);

ENDCOMPONENT;

SIGNALA,B,C,D,seg:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALe:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

U0:

COU4PORTMAP(CLK,RESET,ENA,A,B,C,D);

U1:

mux4_1PORTMAP(A,b,c,d,e,seg);

U2:

counter4PORTMAP(CLK1,e);

U3:

seg7PORTMAP(seg,seg1);

sel<=e;

ENDX47;

六、对程序编译,仿真

1、对4位十进制计数器的程序进行编译,其结果如下:

2、对显示译码段编译、仿真,其结果如下:

3、对整体进行全局编译、引脚分配、波形仿真,其结果如下:

七、VHDL源文件下载到实验箱:

八、设计总结

在本次设计中,我们还需要大量的以前没有学到过的知识,于是图书馆和INTERNET成了我们很好的助手。

在查阅资料的过程中,我们要判断优劣、取舍相关知识,不知不觉中我们查阅资料的能力也得到了很好的锻炼。

我们学习的知识是有限的,在以后的工作中我们肯定会遇到许多未知的领域,这方面的能力便会使我们受益非浅。

在设计过程中,总是遇到这样或那样的问题。

有时发现一个问题的时候,需要做大量的工作,花大量的时间才能解决。

自然而然,我的耐心便在其中建立起来了。

为以后的工作积累了经验,增强了信心。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 太原 理工大学 EDA 十进制 计数 显示器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《Java程序设计》考试大纲及样题试行.docx

《Java程序设计》考试大纲及样题试行.docx