微机0711期中试题.docx

微机0711期中试题.docx

- 文档编号:10165023

- 上传时间:2023-02-09

- 格式:DOCX

- 页数:39

- 大小:173.32KB

微机0711期中试题.docx

《微机0711期中试题.docx》由会员分享,可在线阅读,更多相关《微机0711期中试题.docx(39页珍藏版)》请在冰豆网上搜索。

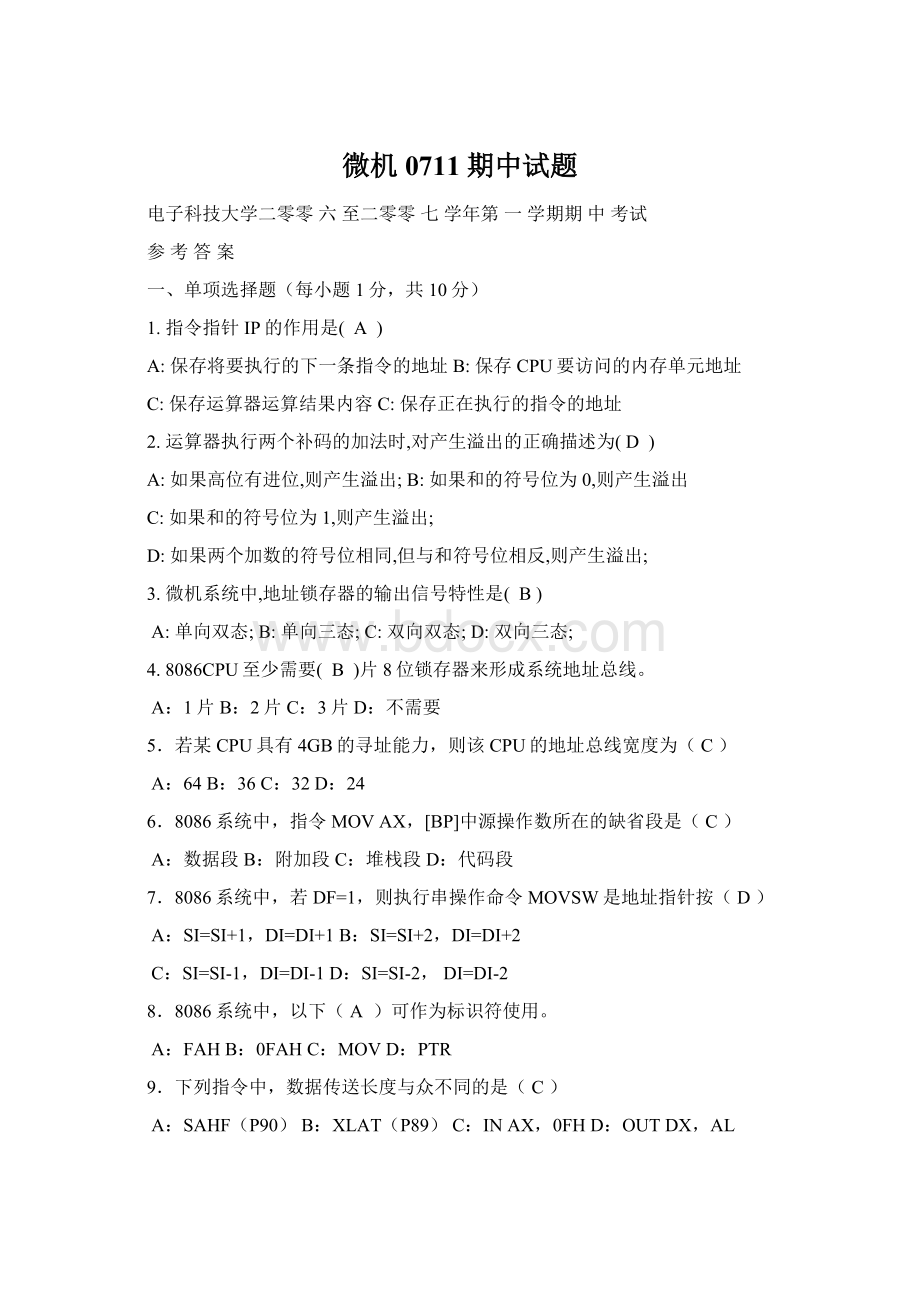

微机0711期中试题

电子科技大学二零零六至二零零七学年第一学期期中考试

参考答案

一、单项选择题(每小题1分,共10分)

1.指令指针IP的作用是(A)

A:

保存将要执行的下一条指令的地址B:

保存CPU要访问的内存单元地址

C:

保存运算器运算结果内容C:

保存正在执行的指令的地址

2.运算器执行两个补码的加法时,对产生溢出的正确描述为(D)

A:

如果高位有进位,则产生溢出;B:

如果和的符号位为0,则产生溢出

C:

如果和的符号位为1,则产生溢出;

D:

如果两个加数的符号位相同,但与和符号位相反,则产生溢出;

3.微机系统中,地址锁存器的输出信号特性是(B)

A:

单向双态;B:

单向三态;C:

双向双态;D:

双向三态;

4.8086CPU至少需要(B)片8位锁存器来形成系统地址总线。

A:

1片B:

2片C:

3片D:

不需要

5.若某CPU具有4GB的寻址能力,则该CPU的地址总线宽度为(C)

A:

64B:

36C:

32D:

24

6.8086系统中,指令MOVAX,[BP]中源操作数所在的缺省段是(C)

A:

数据段B:

附加段C:

堆栈段D:

代码段

7.8086系统中,若DF=1,则执行串操作命令MOVSW是地址指针按(D)

A:

SI=SI+1,DI=DI+1B:

SI=SI+2,DI=DI+2

C:

SI=SI-1,DI=DI-1D:

SI=SI-2,DI=DI-2

8.8086系统中,以下(A)可作为标识符使用。

A:

FAHB:

0FAHC:

MOVD:

PTR

9.下列指令中,数据传送长度与众不同的是(C)

A:

SAHF(P90)B:

XLAT(P89)C:

INAX,0FHD:

OUTDX,AL

10.物理地址为193A1H的内存单元中存放了1个字数据,8086对它进行读操作时至少需要(B)个总线周期。

A:

1个B:

2个C:

3个D:

4个

二、填空题(每空0.5分,共15分)

1.微机系统中的“三总线”通常指(),()和()

(答案无顺序)地址总线(或AB);数据总线(或DB);控制总线(或CB)

2.8bit符号数据可表达的十进制数值范围为(),16bit符号数可表达的十进制数值范围为()。

以补码形式表示的8bit符号数11111000B的十进制真值为()。

-128~+127;-32768~+32767;-8

3.8086CPU指令通常包含()和()两部分。

(答案无顺序)操作码;操作数

4.8086系统中存储单元的物理地址用()位二进制数表示;逻辑地址由()和()两部分构成,均以()位二进制数表示。

20;段基址(段首址);段内偏移量;16

5.与指令LEAAX,BUF功能等价的指令为()。

MOVAX,OFFSETBUF

6.RET指令实现段间返回时,将从堆栈中依次弹出寄存器()和()值。

IP;CS

7.8086CPU中,功能部件()和()可构成二级流水线结构。

(答案无顺序)EU(或执行部件);BIU(或总线接口部件)

8.CPU执行程序的过程,实际上就是周而复始地进行(),(),()的操作。

取指令;指令译码(或分析指令);执行指令

9.8086CPU执行指令OUTDX,AL时,引脚M//IO,/RD,/WR,/DR//T在其有效时刻的电平高低分别为:

(),(),(),()。

低;高;低;高

10.构建4KB容量的存储体,需要()个1K╳4bit的存储芯片,这些芯片应分成()组。

8;4

11.相比DRAM而言,SRAM的集成度较(),存取速度较(),成本较()。

在现代微机系统中,SRAM常用来构成()。

低;快;高;Cache(高速缓存)。

三、判断改错(每小题1分,共10分)

1.若要求系统中所有存储单元的物理地址没有重叠,应使用线选法来产生存储芯片的片选信号。

(×)应使用全译码法产生片选信号

2.CPU对存储器和I/O端口统一编址时不需要诸如IN,OUT这样专用于访问I/O空间的指令。

(√)

3.8086的一个总线周期中,被传送的数据总是在其中的第3个时钟周期出现在总线上。

(×)写操作中,数据从第2个时钟周期开始就出现在总线上

4.8086的堆栈和指令队列都是按照先进后出的原则组织的。

(×)堆栈操作先进后出,指令队列则是先进先出

5.8086CPU上电复位后,执行的第一条指令的物理地址为0FFFF0H。

(√)

6.8086系统中,字数据的低字节一定放在偶地址,高字节一定放在奇地址。

(×)字数据可以非规则存放,但低字节一定放在较低地址,高字节一定放在较高地址

7.Cache-主存,主存-辅存结构的主要目的都是为了尽可能提高访问速度。

(×)主存-辅存结构的主要目是为了增加存储容量

8.8086CPU的ALE引脚总是在总线周期的第一个T状态内输出高电平。

(√)

9.汇编程序是用户使用汇编语言编写的应用程序。

(×)汇编程序是将用户编写的汇编语言源程序翻译为目标代码的程序

10.当计算机主频确定后,地址线愈多则处理数据的能力愈强。

(×)数据线条数愈多,并行处理数据的能力愈强

四、简答题(每小题5分,共20分)

1.对于分时复用地址,数据引脚的CPU,在形成系统三总线时,地址线为什么需要锁存,数据线为什么需要缓冲?

在地址、数据分时复用线上,地址信息总是先于数据产生,且(1’)在访问外部存储器或I/O端口期间应保持不变。

因此需要锁存地址,(2’)以确保当复用线上传送数据信息时,被访问单元的地址仍锁定在锁存器上。

对于数据线,(2’)为了保证多个设备共享总线,应使用总线收发器等器件使各设备在被选通时与总线接通、未被选通时与总线挂断。

2.8086CPU在寻址存储器时为什么需要分段?

(2’)8086共有20条地址线,最大可寻址的存储器空间为220(1MB)。

(2’)但CPU内部的寄存器最大宽度为16位,无法使用任何一个寄存器实现对20位存储空间的访问。

因此(1’)将1MB空间分为若干个逻辑段,每个段的大小不超过216,这样就可以使用1个段寄存器和1个其它寄存器实现20位空间的访问。

3.什么是8086CPU的最小工作模式和最大工作模式?

两种模式的主要区别是什么?

最大/最小工作模式是按照CPU所在系统的规模大小来区分的:

(2’)系统中仅有单CPU时,工作于最小模式;系统中有多个CPU时,工作于最大模式。

最小/最大模式的主要(3’)区别在于系统控制总线形成的方式:

最小模式下,CPU引脚就是控制总线;最大模式下,必须通过总线控制器8288形成控制总线。

4.8086宏汇编语言中,变量和标号有什么异同?

相同之处:

(2’)实质都是代表存储器单元,都具有段基址、偏移量和类型三个属性。

不同之处:

(1)(1’)变量的类型是它所占的存储单元字节数,可能取值1、2、4等;标号的类型是Far、Near两种,表示该标号与使用它的控制转移指令在不同或同一个代码段内。

(2)(2’)变量的段基址可以是任一个段寄存器的值;标号的段基址只是代码段的值。

五、程序填空(每小题5分,共15分)

段内偏移量

内容

0000H

‘A’(或41H)

0001H

‘C’(或43H)

0002H

?

0003H

?

0004H

0005H

0006H

0007H

0008H

1

0009H

1

000AH

1

000BH

1

图1

地址2’,内容3分’

1.已知某数据段的定义如下.请在图1中标明各

有关内存单元的段内偏移量及内容。

DSEGSEGMENT

A1DB‘AC’

A2DW?

CNTEQU$-A1

ORG0008H

A2DBCNTDUP

(1)

DSEGENDS

逻辑地址

内容

SS:

005EH

标号NEXT的偏移量

SS:

005FH

标号NEXT的偏移量

SS:

0060H

62H

SS:

0061H

00H

SS:

0062H

34H

SS:

0063H

12H

SS:

0064H

图2

地址2’,内容3’。

段基址未标酌情扣分。

地址正确,但未写出005E、005F单元内容的酌情扣1分。

2.已知一段指令序列如下。

请在图2中标明CALL指令执行后,堆栈中各有关单元的地址及内容

MOVSP,0064H

MOVAX,1234H

PUSHAX

MOVBP,SP

PUSHBP

CALLAX

NEXT:

……….

3.以下是通过逻辑移位和加法实现乘法的程序段。

已知一个字节变量X,要求通过以下指令实现X*12,乘积(假定仍为1字节)存回原变量处。

试在横线上添加适当的8086汇编语言指令或操作数。

MOVAL,X

MOVCL,2(或3)

SHLAL,CL

MOVBL,AL

SHLAL/BL,1(或SHRAL/BL,1)

ADDAL,BL

MOVX,AL

六、读程序并回答问题(每小题5分,共10分)

1.阅读下列程序段,并回答问题:

在何种条件下,(AH)=0?

BEGIN:

INAL,5FH

TESTAL,80H

JZBRCHI

MOVAH,0

JMPSTOP

BRCHI:

MOVAH,0FFH

STOP:

………….

当由地址为5FH的I/O端口读入的字节数值为负时,(AH)=0未标明端口操作的酌情扣1’

2.阅读下列程序,并回答问题:

该程序段完成什么功能?

MOVCX,100

LEASI,BUF

MOVSUM,0

MOVAH,0

NEXT:

MOVAL,[SI]

CMPAL,0

JGENXT

NEGAL

NXT:

ADDSUM,AX

INCSI

LOOPNEXT

求100个字节符号数的绝对值的和,并存放在SUM字单元未标明绝对值操作的酌情扣1’

七、应用编程(每小题10分,共20分)

1.编写一个完整的汇编语言源程序:

数据段中以string开始处存放着一个含10个字符的字符串,搜索串中是否有空格。

如果没有空格,通过屏幕显示“NoSpace”;如果有空格,则显示“GotSpace”。

DATASEGMENT;数据段定义正确3’

stringDB10DUP(?

);字符串,具体字符略

str1DB‘NoSpace!

$’

str2DB‘GotSpace!

$’

DATAENDS

STACKSEGMENTPARASTACK‘SATCK’

DB100DUP(?

)

STACKENDS

CODESEGMENT;代码段定义及程序返回正确2’

AASUMECS:

CODE,SS:

STACK,DS:

DATA,ES:

DATA

BEGIN:

MOVAX,DATA;初始化正确2’

MOVDS,AX

MOVES,AX

MOVAL,20H;空格的ASCII码AL

LEADI,string

MOVCX,10

CLD

REPNESCASB;串搜索操作正确1’

JEFOUND;跳转处理正确1’

LEADX,str1;未找到空格

JMPNEXT

FOUND:

LEADX,str2;找到空格

NEXT:

MOVAH,9;显示信息正确1’

INT21H

MOVAH,4CH

INT21H

CODEENDS

ENDBEGIN

2.某CPU有8位数据线,16位地址线,控制信号/RD,/WR分别表示总线读有效,写有效。

M//IO为高时表示访问存储器空间。

请采用4KX8的RAM芯片来设计总容量为16KB的存储器系统。

要求该存储系统占用地址空间为4000H~7FFFH

(1)该存储系统共需多少片4KX8的RAM芯片?

这些RAM芯片分成多少组,每组多少片?

(2’)4片;4组,每组1片;(2’)地址空间见图。

(2)该存储系统需要多少根地址线用于片内单元选择(字选)?

多少根地址线用于片选译码?

(2’)需12根低位地址线进行片内译码,剩余4位高位地址线进行片选全译码。

(3)根据

(1)

(2)画出存储芯片与系统总线的连接示意图。

片选译码电路请采用一片74LS138及必要的门电路来实现。

数据线正确1’,A0~A11正确1’,74LS138输入(A12~A15以及M//IO)正确1’,74LS138输出(4个片选)正确1’

电子科技大学二零零七至二零零八学年第一学期期中考试

一、选择题答案(每空1分,共15分)

1

2

3

4

5

6

7

8

(1)

8

(2)

9

(1)

9

(2)

10

11

(1)

11

(2)

11(3)

C

A

D

D

C

B

C

A

C

A

B

BDE

CDE

B

D

二、填空题答案(每空2分,共20分)

1.181,5(视为非组合BCD码时高4位无效),-75

2.用于锁存有效地址信号(地址锁存使能信号),以分离时分复用的地址信号和数据信号

3.59B0H,3060H

4.10101011,10000100

5.操作码,操作数

一、选择题(每空1分,共15分)(除特别指明外均为单项选择。

)

1.n+1位符号数x的补码表示范围为()。

A.-2n<x<2nB.-2n≤x≤2n

C.-2n≤x<2nD.-2n<x≤2n

2.8086CPU用于中断请求输入的引脚信号是()。

A.INTR和NMIB.INI和NMIC.INTR和INTAD.INTE和INET

3.CPU的字长通常与其()一致。

A.寄存器个数B.I/O端口数C.地址线宽度D.数据线宽度

4.8086CPU中指令指针寄存器IP通常用于存放()。

A.已被译码的指令的条数B.正被译码的指令的条数

C.正在执行的指令的地址D.下一条将要取出的指令的地址

5.使用基址寻址方式时,CPU实际是从()处获取操作数的。

A.数据寄存器B.地址寄存器C.存储器D.IO端口

6.宏指令与子程序的相同之处为()。

A.宏指令的目标代码与子程序的目标代码都是唯一的

B.都需要先定义,后调用

C.执行宏指令的目标代码时与子程序时一样,都需要增加如保护、恢复现场类的额外开销

D.宏指令的目标代码与子程序的目标代码都不是唯一的

7.MIPS用来描述计算机的运算速度,含义是()。

A.每秒处理百万个字符B.每分钟处理百万个字符

C.每秒执行百万条指令D.每分钟执行百万条指令

8.8086与外部进行数据交换时,会在(

(1))时刻发出地址信号,并在(

(2))时刻检测Ready信号以确定是否进入等待周期。

A.T1B.T2C.T3D.T4

9.8086系统中,符号数和无符号数使用(

(1))的加减法指令;使用(

(2))的乘除法指令。

A.相同B.不同C.视情况而定

10.(可多选)由汇编语言源程序得到计算机可执行的程序,必须经过的过程包括()。

A.综合B.汇编C.验证D.链接E.编译

11.(可多选)下列存储器中,断电后内容仍然可以保存而不丢失的存储器包括(

(1)),需要动态刷新的存储器包括(

(2)),需要紫外光才能擦除的存储器包括((3))。

A.SRAMB.DRAMC.FLASHD.EPROME.EEPROM

二、填空题(每空2分,共20分)

1.8位二进制数10110101,视其为无符号数时,表示的十进制数为;视其为BCD码时,表示的十进制数为;视其为带符号补码时,表示的十进制数为。

2.8086CPU上ALE引脚信号的作用是。

3.设(SS)=59B0H,(SP)=305AH,若从堆栈中取出3个字数据,则(SS)=H,(SP)=H。

4.设十进制带符号数X=-85,Y=39,则用8位二进制表示:

[X]补=,[X-Y]补=。

5.一条微处理器指令包括和两部分。

三、简答题(每小题6分,共36分)

1.试述8086CPU的结构特点。

它是如何适应流水线操作的?

8086CPU内部分为EU和BIU两部分,并通过指令队列和内部总线相连。

(2分)

其中BIU单位经外部总线从程序存储器中读取指令并放入指令队列缓冲器,EU单元从指令队列缓冲器中获取指令并执行的功能。

(2分)

而指令队列缓冲使取指和执指能同时操作,适应指令流水线操作,提高了CPU的效率。

(2分)

2.简述8086CPU的存储器分段管理方式,并给出逻辑地址LA和物理地址PA之间的关系。

8086共20根地址线(最大可寻址1MB存储空间),但其内部只能处理16位地址(直接寻址空间仅为64KB),因此需要将整个存储空间分成若干个不超过64KB的逻辑段。

(2分)

针对这种分段管理方式给出的存储单元逻辑地址LA由段基址(16bit)和偏移量(16bit)两部分组成,而存储单元物理地址PA指真正的20位硬件地址。

两者之间的关系是:

(4分)

●PA=段地址×16+偏移地址

●每一个PA可能对应不止一个LA,而每一个LA对应唯一的一个PA

3.已知(AX)=0110010110100100b,(BX)=1010001010011010b,指令SUBAX,BX执行后,求各个状态标志位的值及相关寄存器的值。

(AX)=1100001100001010,(BX)=1010001010011010(2分)

SF=1,OF=1,CF=1,PF=1,AF=1,ZF=0(4分)

4.已知DS=8000H,ES=7000H,SS=6000H,BP=9400H,SI=0E370H,AX=4B08H,

●说明指令MOV[BP+SI+31A3H],AX的源、目的操作数的寻址方式;

●画出指令的寻址过程示意图,并说明相关寄存器、存储器单元的值;

该指令源操作数为寄存器寻址,目的操作数为带位移量的基址加变址寻址。

(2分)

寻址过程如下:

(EA正确2分,PA正确1分,存放正确1分)

5.8086系统中存储器为什么要采用奇偶库结构?

系统如何区分两个不同的库?

这种结构对数据存放有什么影响?

8086CPU的存储系统中规定每个存储单元(地址)仅存放8位二进制信息;而8086CPU数据总线的宽度为16位,即8086可能进行8位读写操作,也可能进行16位读写操作。

为解决这个问题,8086系统中的存储器采用奇偶库结构。

(2分)

8086CPU分别使用/BHE信号和A0信号使能奇、偶地址库,且均为低电平有效:

(2分)

其数据存取特点是:

(2分)

●奇地址字节数据:

一个总线周期可完成传送,此时/BHE=0,A0=1。

●偶地址字节数据:

一个总线周期可完成传送,此时/BHE=1,A0=0。

●16位规则字数据:

即偶地址存放低8位,奇地址存放高8位时,用一个总线周期可完成16位传送。

此时/BHE=0,A0=0。

●16位非规则字数据:

即偶地址存放高8位,奇地址存放低8位时,需两个总线周期才可完成16位传送。

6.试说明指令、伪指令及标识符在8086宏汇编语言中的作用。

●指令助记符将被汇编程序翻译为指令机器码,是整个程序的主体,运行时由8086CPU执行;(2分)

●伪指令助记符主要用于给汇编程序提供足够的补充管理信息,以便汇编后能获得正确完整的目标代码,汇编后伪指令不会生成任何结果。

(2分)

●标识符通常即为符号地址,主要用于程序书写及调试方便,汇编后即用真实地址替换。

(2分)

四、程序阅读理解(每小题6分,共12分)

1.已知(AL)=56H,下列程序执行之后,(AL)=38H(或56),(DL)=06H(或6),该程序段实现的功能是将AL中存放十进制数(组合BCD码)转换为二进制(十六进制)。

MOVDL,AL

ANDDL,0FH

ANDAL,0F0H

MOVCL,4

SHRAL,CL

MOVBL,10

MULBL

ADDAL,DL

2.根据下列数据段定义完成存储单元的分配。

存储单元偏移地址

存储单元内容

……

(AB1)1000H

?

1001H

?

(AB3)1002H

20H

1003H

10H

1004H

10H

1005H

10H

(AB4)1006H

02H

1007H

10H

……

DATASEGMENT

ORG1000H

AB1DW?

AB2EQU03H

AB3DB20H,AB2DUP(10H)

AB4DWOFFSETAB3

DATAENDS

五、编写程序(17分)

1.(10分)设有100个字节数据(补码)存放在数据段中EA=4000H的存储单元中。

试从该数据区中找出最小的一个并存入EA=4100H单元中,请编写完整的8086宏汇编语言程序完成该功能。

DATASEGMENT;数据定义(3分)

ORG4000H

TABDB100DUP(?

)

COUNTEQU$-TAB

ORG4100H

RESULTDB?

DATAENDS

;---------------------------------------------------------------------------------

CODESEGMENT;定义、返回及初始化(2分)

ASSUMECS:

CODE,DS:

DATA,ES:

DATA

STARTPROCFAR

PUSHDS

MOVAX,0

PUSHAX

MOVAX,DATA

MOVDS,AX

MOVES,AX

;---------------------------------------------------------------------------------

MOVSI,OFFSETTAB;循环(2分)

MOVCX,COUNT-1

MOVAL,[SI]

AGN:

INCSI

CMPAL,[SI]

JLELOOP1;带符号数比较(2分)

MOVAL,[SI]

LOOP1:

LOOPAGN

MOVRESULT,AL;保存结果(1分)

RET

CODEENDS

2.(7分)试编写一个过程程序,其功能为:

将AL(入口参数)中的组合BCD码在显示屏上显示。

要求必须有足够的注释说明。

;名称:

BCD码显示子程序BCDDISP;注释说明(1分)

;功能:

将指定的2位组合BCD码显示在显示屏上

;参数:

入口参数(AL),用于存放2位组合BCD码;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 微机 0711 期中 试题

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx