高速设计指导.docx

高速设计指导.docx

- 文档编号:10157564

- 上传时间:2023-02-08

- 格式:DOCX

- 页数:45

- 大小:670.67KB

高速设计指导.docx

《高速设计指导.docx》由会员分享,可在线阅读,更多相关《高速设计指导.docx(45页珍藏版)》请在冰豆网上搜索。

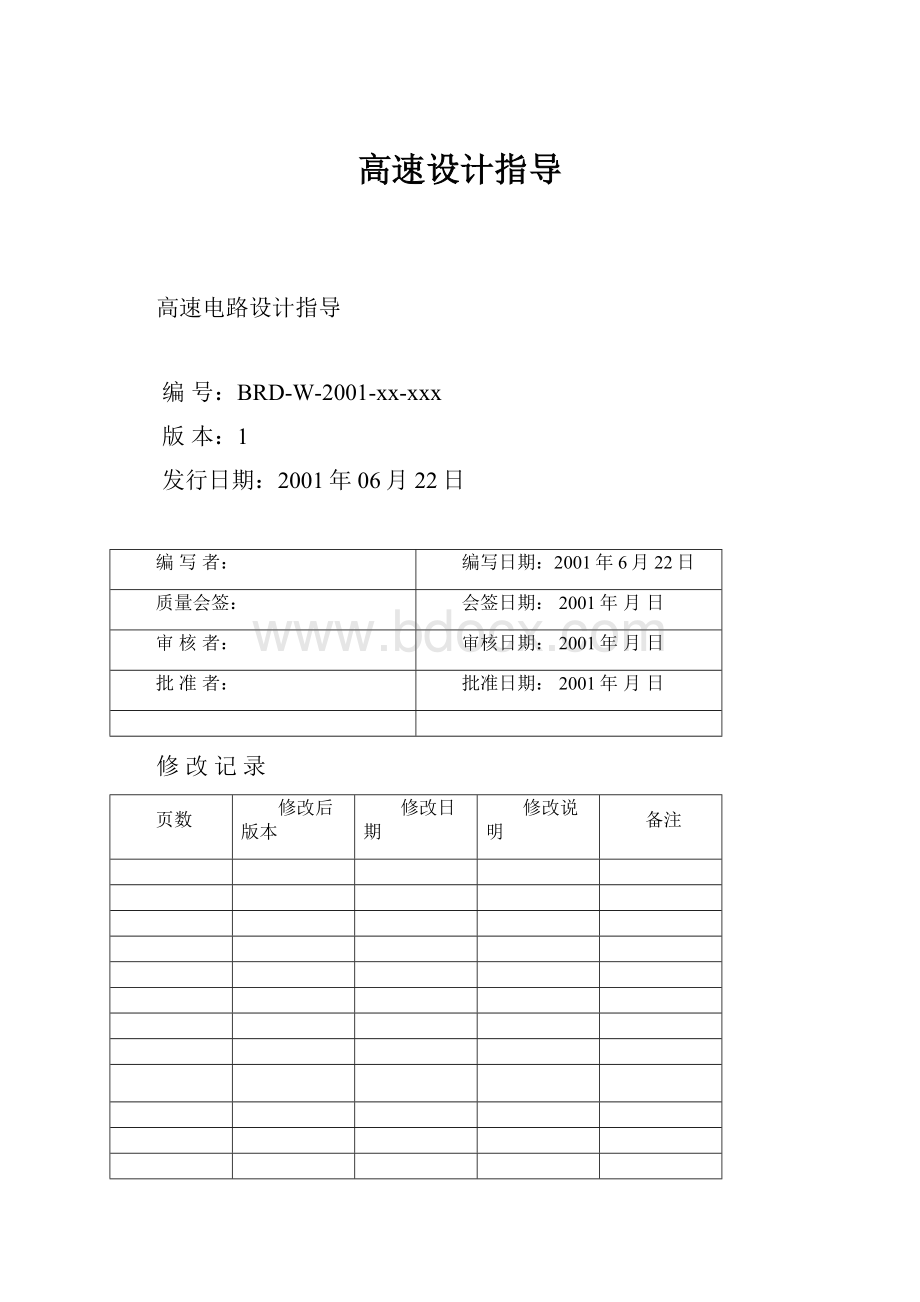

高速设计指导

高速电路设计指导

编号:

BRD-W-2001-xx-xxx

版本:

1

发行日期:

2001年06月22日

编写者:

编写日期:

2001年6月22日

质量会签:

会签日期:

2001年月日

审核者:

审核日期:

2001年月日

批准者:

批准日期:

2001年月日

修改记录

页数

修改后版本

修改日期

修改说明

备注

发行范围

单位

说明

□全中心

□中心主任

□策划部

□研发部

□综合管理部

□测试部

□项目组

□技术组

□项目管理组

□质量管理组

□其他

附录1表格索引

附录2图片索引

1引言

1.1编写目的

为规范IP产品部的高速电路的基本设计规则,从而尽可能减少因高速设计不合理而出现的硬件问题,同时便于整个设计工作的管理和问题的查找及解决。

1.2发行范围

研发中心IP产品部

1.3使用范围

本高速电路设计指导中包含的规则都是针对一般性情况,如果一些具体器件有特殊要求,以相应的芯片厂家给出的应用参考设计为准。

1.4名词解释

Chasisground保护地;机壳地

2高速电路的基本概念

高速设计中的高速是一个相对概念,而不仅仅是以工作的时钟频率来进行划分。

如果所设计系统的工作环境使得其中器件的交流特性对系统性能有较大影响时,这个系统就应该作为高速电路来考虑。

2.1信号的上升时间与带宽的关系

图2-1方波信号时间参数及频谱分布

其中:

tr——上升时间

td——下降时间

T——信号脉宽

从信号频谱图上可以看到:

频率0.5/T对应信号的3dB带宽,而信号能量大部分集中在0.5/tr或0.5/td(称为转折频率)频段范围内。

频率大于0.5/tr或0.5/td时,信号强度迅速减少。

2.2高速电路判定的基本原则

基于2.1中得出的信号的上升时间与带宽的关系,可以得到高频电路判定的原则为:

在信号的转折频率点0.5/tr或0.5/td处,如果器件的寄生效应(如寄生电感、电容等)和(或)连接线的交流特性不能再忽略不计时(即连接线必须作为传输线来处理时),电路应该作为高速电路处理。

如寄生串联电感,其阻抗为ZL=

,当f增加,ZL也增大。

判定时,可以通过信号的上升时间或下降时间计算出转折频率作为f,计算ZL。

如果ZL达到一定值,即与器件的输入电阻或输出电阻相比不能再忽略不及时,就应该考虑寄生串联电感带来的分压、串扰等高速问题了。

其它,如引脚电容则会使信号的上升时间增大、信号线的等效阻抗降低、造成阻抗补匹配而导致信号反射等。

至于信号线作为传输线处理的判定条件将在第4节中给出。

3适合高速电路的板材

高速电路由于其特殊性,与低速电路相比,对制作的板材也有一定要求。

目前国内已有的可用在高速电路方面的材料有:

FR4、Rogers4000系列和HITACH的MCL-LX-67(基材)GXA-67N(固材)。

下表中列出了几种适合制作高速电路板的材料及其应用范围的比较(这些材料昆山沪士均可以提供)。

表3-1几种高频制板材料及其使用范围

材料名

类型及型号

相对介电常数(

)

(1GHz时测量)

适用的频率范围

描述

FR4

普通FR4

4.3

<2.5GHz(5Gbps)

适合一般PCB板的要求,损耗较大,花费比较便宜

NelcoN4000-6

NelcoN4000-7

4.3

<2.5GHz(5Gbps)

改良型的FR4,这两种材料做出的板耐高温冲压,适合做背板,花费比较便宜

NelcoN4000-13

3.8~3.9

<5GHz(10Gbps)

具有较小的适合相对介电常数,更高速的电路板,适合高速背板,花费适中

Rogers

RO4350(基材)

RO4003(固材)

3.6

<10GHz(20Gbps),RF范围

损耗小,适合制作高速电路板,花费较高为FR4的2倍

Hitachi

MCL-LX-67(基材)

GXA-67N(固材)

3.44

<10GHz(20Gbps)

RF范围

损耗小,花费高,而且加工12层以上的板目前国内有一定技术问题

表4-1不同信号线对应的单位长度延迟时间及特性阻抗值

连接线

特性阻抗()

D延迟时间(ps/in)

适用范围

同轴线

d2>d1

双绞线

s>d

微带线

t/H<<1

0.1 1< <15 带状线 对于阻抗公式要求: W/b<0.35 t/b<0.25 注: 1oz1.4mil 4传输线基础 由于信号的上升时间越来越短,如果上升时间小于一定值,当信号翻转时,各器件之间的信号线就不能再作为理想的连接线处理了,而应该作为传输线考虑。 传输线效应是高速信号线的一种瞬时特性。 4.1传输线的判定准则 信号线作为传输线处理的判定主要由线上信号的上升时间、信号线结构、长度和采用介质的相对接介电常数 等决定。 信号线上的信号上升边对应的长度(电长度,可以理解为在Tr时间内,信号线上信号可传输的长度)可以由下面的公式决定: (4-1) 其中lr为上升边对应的电长度, 为上升时间(单位: ps),D为信号线单位长度的延迟时间(单位: ps/in.)。 如果连接线的长度Llr/6,则连接线必须作为传输线考虑,既必须考虑其特性阻抗(分布电容和电感)。 表4-1中给出了不同信号线对应的单位长度延迟时间及特性阻抗值。 目前常用的PCB板上传输线模型包括微带线(主要是顶层和底层的走线)和带状线(主要是中间层的走线)两类。 一般如果时钟频率超过了50MHz,时钟线最好选用带状线方式。 4.2常见传输线的参数计算公式 表4-1中给出的计算微带线和带状线特性阻抗的公式都是近似公式,更准确的计算式在下面给出。 4.2.1微带线 对于0 <16,误差<2%。 (4-2-1) 其中 为微带线模型中介质的等效介电常数。 (4-2-2) (4-2-3) 4.2.2带状线 对于t/b<0.25,t/W<0.11的对称结构(H1=H2)的带状线,计算误差<1.3%。 当W/b0.35时, (4-3-1) (4-3-2) 当W/b>0.35时 (4-4-1) (4-4-2) 4.3传输线最大允许线长的估算 表4-1中已经给出了各种传输线的单位长度延迟时间D,如果给定最大延迟时间tdmax,由此可以估算最大允许的线长为: (4-5) 如果要求最大延迟时间不能超过1ns,由上面的公式可以计算出只考虑延迟时间的最大线长限制。 表4-2中给出了最大延迟为1ns时,几种材料对应的最大线长。 表4-2几种材料1ns时延允许的最大线长度 材料类型 r Lmax(mm) 微带线 带状线 FR4 4.3 181.4 144.1 3.8~3.9 188.1 151.3 Rogers 3.6 193.7 157.4 Hitachi 3.44 196.8 161.1 这里只考虑了单纯由传输线长引起的延迟,考虑到过孔等其它因素,最大线长应该更小。 设计原则是线长应该尽可能短。 5LVDS信号线 LVDS(LowVoltageDifferenceSignaling)的全名为低电压插分信号。 由于采用这种信号方式的电路功耗低,产生的噪声低,抗共模干扰强,与传统的TTL电平相比传输速率可以达到很高的特点。 LVDS可用于点到点结构和多点结构中。 目前LVDS技术已经越来越广泛的使用在高速设计中。 5.1点到点LVDS LVDS构成的点到电路拓扑结构为: 图5-1LVDS点到点电路结构 每路信号由两条信号线组成。 LVDS差分线差分阻抗通常应为10010%(90~110)。 LVDS必须在接受器端加端接负载。 5.1.1LVDS的端接方式 其中端接负载的方式有: (a)单电阻(b)电阻加电容 图5-2LVDS接受端的端接方式 其中最常用的是(a)中的端接法。 对于端接负载的要求为: (1)电阻最好使用表贴电阻。 (2)负载与接受器(Receiver)间的间距应该<7mm。 (3)电阻误差应该为1~2%以内。 (4)采用(b)中的端接法,是为了更好的滤除共模噪声。 C50pF。 注意: 有的芯片在内部集成了端接负载,因此外面不需要另外再加端接负载。 具体设计时应仔细参考芯片的数据手册。 5.1.2LVDS差分线可采用的传输线类型 LVDS可以采用微带线和带状线两种结构。 从屏蔽效果方面考虑,带状线的屏蔽效果更好,EMI影响低得多,通常1Gbps以下的数据可以用微带线结构,高于1Gbps应该用带状线结构。 带状线可以采用边缘耦合带状线(eadge-coupledstripline)和宽边耦合带状线(Broasidestripline)。 但是采用考虑板的厚度,一般采用边缘耦合带状线。 其结构示意图如图5-3(b)所示。 图5-3(a)微带线LVDS结构示意图 图5-3(b)边缘耦合LVDS结构示意图 5.1.3几种不同材料对应的LVDS差分线对特性阻抗 对于采用微带线结构,选定LVDS尺寸为: S=15mil,t=1.4mil(1盎司)。 对应不同材料,可选择的尺寸与差分电阻的对应关系见表5-1(可供设计参考)。 对于带状线结构,选定LVDS尺寸为: S=15mil,t=1.4mil(1盎司)。 对于选定的LVDS,计算了几种材料对应的差分线宽度与差分阻抗关系见表5-2(可供设计参考)。 表5-1不同材料,微带LVDS差分阻抗与尺寸的关系(S=15mil,t=1.4mil(1盎司)) 材料类型 r H(mm) W(mil) 差分特性阻抗() FR4 4.3 0.176 9~12 106.2~92.3 0.2 10~12 107.1~98 0.254 12 107.9 3.8~3.9 0.176 10~12 105.2~96.2 0.2 11~12 106.5~102 Rogers RO4003 3.6 0.203 11.5~12 108.3~106.1 Hitachi GXA-67N 3.44 0.2 11.5~12 108.5~107.3 注: 采用微带线结构时,为了降低EMI问题,可在每对差分线对之间加地屏蔽线。 表5-2不同材料,带状线LVDS差分阻抗与尺寸的关系(S=15mil,t=1.4mil(1盎司)) 材料类型 r H1(mm) H2(mm) W(mil) 特性阻抗() FR4 4.3 0.296 0.254 8 91.4 0.285 0.3 8 93.9 0.3 0.3 8 95 3.8~3.9 0.296 0.254 8 96.6 0.285 0.3 8 99.3 0.3 0.3 8 100.4 Rogers 3.6 0.3 0.25 11 90.6 Hitachi 3.44 0.2 0.4 11 90.6 0.3 0.26 11 93.6 5.1.4LVDS设计规则 LVDS尺寸的选定规则: (1)差分线长匹配原则 差分线长度的不同,将引起差分线对的两个线号线间的相差,从而引起电磁干扰(EMI)。 对于采用边缘耦合带线结构的差分线对,同一差分对的两个信号线间的相差可以按照下面的公式计算: (度)(5-1) 其中,c= mm/s(自由空间中的光速),f(Hz)为工作频率, 为采用PCB板材的相对介电常数, (mm)为差分对两信号间的长度差。 两信号间的相差不能超过信号上升或下降时间对应的相差 ,其中 (s)为上升时间, (s)为下降时间。 要保持差分线好的一致性,两线间的相位差最好满足: ,即 ,如果采用微带线结构,式中的 用 (有效介电常数)替代。 对于采用的Vitesse870/880芯片组,其CML输出信号的上升和下降时间均为100ps,可以计算出两种不同材料对应的带状线结构差分线对两信号间的长度差(见表5-3)。 如果采用微带线,允许的l可以大些。 表5-3两种不同材料对应的差分线对两信号间的长度差要求 材料类型 r l(mm) FR4 4.3 <1.74 3.8~3.9 <1.92 Rogers 3.6 2.08 NEC 3.44 2.18 注: 这里采用的CML输出信号上升和下降时间均为100ps,交换速率为2.125Gbps (2)差分线各参数应满足的关系: 线间距S<2W,差分对间的距离xmax(2W,2S)。 (3)为了减少对其它信号(如TTL和CMOS)的干扰,应该保持其它非LVDS信号与差分对信号的距离>max(3W,3S)。 (4)如果使用了保护地线或地填充块,则距离最近的差分距离至少应该>max(2W,2S)。 (5)确定差分线尺寸时,最好先确定线间距S(可以根据制板厂家可以提供的最小线间距作为参考),然后根据选择的板材来确定差分线的宽度。 布线技巧 (1)AMP公司推荐,对于PCB板、信号线和参考地(信号地或电源)最好采用1oz铜箔,比薄尺寸的铜箔的信号质量要好。 (2)对于多层板,过孔在不走信号的层最好不设置焊盘(这可以通过设置内部导体直径比孔直径大2~3mil就可以了)。 5.2BLVDS 上一节讲的LVDS主要针对点到点的电路拓扑结构。 BLVDS(BusLVDS)则应用于多点结构。 与点到点LVDS不同之处在于,BLVDS是专门针对多点结构的,其可提供更大的驱动电流来驱动多点结构中要求的双端接结构。 目前这种BLVDS结构常见的电路拓扑图为: 图5-4BLVDS多点结构 5.2.1National推荐的BLVDS结构 表5-4BLVDS差分阻抗与尺寸的关系(FR4材料,r4.5,t=1.4mil(1盎司)) 插分线结构 H1(mil) H2(mil) H((mil)) S(mil) W(mil) 差分特性阻抗() 微带线 7 7 6 130 带状线 (边缘耦合) 8 8 8 6 100 16 16 13 6 130 13 13 18 6 130 目前BLVDS配套使用芯片的应用最高频率不超过5Gbps,因此板材可以采用FR4材料就可以了。 对于BLVDS,考虑到多点应用的特殊性,尤其是当应用于背板结构中,考虑到分支短线(Stub)的长度、连接器等因素的影响,要求插分对的插分阻抗应该在100~130之间。 表5-4是National公司给出的不同插分信号线结构对应的尺寸与阻抗,可供设计参考。 5.2.2BLVDS的设计规则 BLVDS因为是LVDS的扩展,因此设计时也必须遵守5.1.4一节中给出的LVDS的设计规则。 此外,BLVDS还应该满足以下的设计规则: (1)分支短线的长度必须<0.5inch(13mm),如果是背板结构,要求逻辑插卡上的分支线长度<1inch(25.4mm),且越短越好。 (2)推荐使用插分阻抗为130的微带线或带状线结构。 (3)在满足要求的情况下,尽量选择上升延较慢的器件。 (4)对于选用130的插分阻抗,总线两端的端接电阻应该选择接近80而不是54(对于100插分阻抗而言)。 6电源系统 高速电路设计中的一个关键就是实现低噪声电源分配网络(包括地)。 最好的电源分配系统就是采用电源平面。 6.1电源系统的一般设计规则 电源系统的一般设计规则: (1)各共地芯片间应采用低阻抗地连接(既最好采用地覆层或地网平面),提供低阻抗电流返回路径,从而降低噪声,最好使用实心地平面。 (2)与地引脚一样,各共电源芯片间的电源引脚间应该采用低阻抗连接(既最好采用电源覆层或电网平面,如果采用电源线结构,最好使用尽可能粗的线)。 (3)电源与地之间应该使用低阻抗连接,这可以通过将电源平面和地平面放置在相邻的层实现,同时为了保证在低频时的低阻抗,还应在电源与地之间加合适的旁路电容。 6.2电源去耦 为了降低电源平面的噪声,主要是来自交流分量的干扰,通常还需要对电源进行滤波(加旁路电容)。 6.2.1去耦电容的选择规则 表6-1电容的类型及其主要应用 类型 典型的电容范围 应用 电解电容 (Electrolytic) 1uF~>20uF 通常用于电路板上的电源接入处的去耦 玻璃封装陶瓷电容 0.01uF~0.1uF 用于芯片的旁路电容。 常与电解电容并联使用,以增加滤波的带宽 陶瓷片电容 0.01uF~0.1uF 用于芯片,高度低,适用于对高度有要求的场合 C0G <0.1uF 用于噪声敏感器件的旁路电容,通常与其它陶瓷片电容并联使用,以增加滤波范围 一般的规则为: 在PCB板上,从板外引入电源的输入端应该加上1uF到10uF的电容,目的是滤除来自板外得低频电压(60Hz以内);而在板上每个工作器件的电源和地引脚之间加0.001uF到0.1uF的电容,为了滤除板内工作器件产生的高频电压(通常为100Mhz或更高的频率范围)。 采用将两种不同种类的电容并联方式增加滤波带宽时,由于电容存在等效电感(ESL),因此并联电容在滤波带的某个频率会产生谐振,如果干扰信号的频率正好在这个谐振频率附近,则此时并联电容就起不到滤除噪声的作用了。 其中情况下有两种解决方法: (1)选择合适的电容值,使要滤除的频率范围远离自谐振频率。 (2)使用自谐振频率满足设计要求的单个电容,同时根据需要可以使用多个相同的电容并联,以获得要求的频率范围。 6.2.2去耦电容的一般设计规则 去耦电容的一般设计规则为: (1)尽量保证芯片的每个电源引脚有一个去耦电容。 (2)去耦电容与电源和地引脚之间应该用尽可能粗的线相连。 (3)去耦电容最好与芯片放在同一边(特别是对于时钟器件等高速器件而言,其它非高速器件可根据具体情况而定,也可以放在背面)。 (4)去耦电容应该近可能靠近芯片的电源引脚放置,以尽量降低寄生参数(电感、电容) (5)去耦电容的封装到地芯片的或电源引脚之间的连线长度必须<1/4inch(6.35mm)。 特殊要求应参照芯片厂家提供的参考设计。 6.3数字电源/地与模拟电源/地 6.3.1数字电源与模拟电源 如果器件既有数字电源,又有模拟电源,应该将模拟电源和数字电源隔离开。 但是布线时必须保证单独的模拟电源和数字电源在叠层方向上的投影没有重叠,否则隔离会失效。 最好将电源平面进行分割。 分割的位置最好在器件的下方,且模拟电源平面和数字电源平面之间应该通过一个或多个磁珠相连。 磁珠放置的位置应该满足使电流均匀分布。 选用的磁珠能承受的最大电流应该为实际设计预计流过电流量的150%。 在磁珠的两边应该各接一个大的接地旁路电容(2.2uF~10uF),以防止转换噪声通过磁珠。 此外芯片的每个模拟电源引脚应该加高频旁路电容(0.01uF)。 保持数字电源远离高速信号,变压器和高速连接器。 高速信号应该紧靠地层布线,必要时需加屏蔽措施。 模拟电源和数字电源的分割方法; (a)字电源和模拟电源隔离,(b)数字电源和模拟电源隔离, 数字地和模拟地采用同一个地平面数字地和模拟地也隔离 图6-1数字电源/地平面与数字电源/地平面的分割 注意: 这里应该使用磁珠而不是电感,因为磁珠在DC和很低频率时,阻抗几乎接近于0,相当于小电感或电阻,在低频时没有什么影响。 而在RF时,磁珠呈现高阻抗,直到到达铁磁材料达到其能够工作的最高频率。 因此磁珠是一个大的RF电阻,可以防止RF能量在两个隔离的部分之间传播。 而电感具有电抗jL,这是传输路径中不期望出现的。 同时由于电感具有寄生电容,在某些频率将产生谐振,在这些频率,RF电流将通过电感在两个隔离部分间传播,从而电感失去了对高频的隔离作用。 6.3.2数字地与模拟地 一般情况下,模拟地和数字地可以公用。 但是有的器件可能要求将模拟地和数字地分开。 如果采用分割的模拟地和数字地,在走线时必须注意信号的地反回路径。 如果信号横跨模拟地和数字地,则需要特别注意。 如果确定信号地回路是走模拟地和数字地所在层,则应该在信号线垂直正对的位置处加上小段地连接(称为地桥groundbridge)(如图)。 图6-2模拟地与数字地之间的跨接线由于地返回路径 7端接 一般控制线需要加端接(如时钟输入、SRAMs和FIFOs的读/写选通线)、片选或RAMs、PROMs和PLDs的输出使能信号。 RAMs和PROMs的地址线和数据线通常不需要加端接。 但是如果是重加载,地址和数据线也可以加端接。 双向总线应该在信号线两端加端接,其阻抗应等于信号线的特性阻抗。 7.1源端匹配——串联电阻 串联电阻应尽可能靠近源放置,串联电阻的值一般为10~75,因此DC功耗小。 具体大小可以根据选用的驱动芯片决定,选用的电阻值应满足关系: (即串联终端的阻值Rd等于或略大于连接线的特性阻抗Z0与驱动源的内部电阻之差Rs)。 如果选用的连接线阻抗为50,对于多数情况通常可以使用33串联电阻。 串联电阻只适用于点对点的连接线,对于有分布负载的信号线不能使用串联终端。 图7-1源端匹配电阻 7.2负载端匹配 使用以下终端(除二极管终端以外)均要求终端元件的引出脚尽可能短。 7.2.1简单并联终端 图7-2-1简单并联终端 选择并联阻抗大小等于传输线的特性阻抗,并且应该尽可能靠近负载放置。 这种端接使用的条件是: 负载电流不能超过源芯片的DC工作条件。 负载电流最大值由源输出高电压决定,既 ,只有当 才可以使用简单并联终端。 7.2.2有源并行终端 图7-2-2有源并行终端 Vbias值一般在源的VOH和VOL之间,同时还要求Vbias能够跟上源输出的转换速度,迅速在IOL和IOH之间转换。 这种方法实现比较困难。 7.2.3戴维南并联终端(上拉/下拉并联终端) 图7-2-3戴维南并联终端(上拉/下拉并联终端) R1和R2的选择应该使其等效戴维南电阻满足 。 选择的R2应该保证没有接连接线时,B点的为逻辑高状态,一般使B点电压为高电平门限电压。 R1的最大值由可接受的信号上升时间决定,最小值由源的IOL电流决定。 这种方式DC功耗比较大。 7.2.4串联RC并联终端 图7-2-4串联RC并联终端 此为一般目的终端。 对于Z0=50,R通常取47。 C可以按照下面的方法确定: 令R=47+ROH,ROH为源输出高电平内阻,先由公式 计算C,其中T为允许的最大信号上升或下降时间,然后计算RC

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 高速 设计 指导

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《JAVA编程基础》课程标准软件16级.docx

《JAVA编程基础》课程标准软件16级.docx

四种基本情绪.ppt

四种基本情绪.ppt